T1CDA

Click here to load reader

-

Upload

juan-samuel-vazquez-arteaga -

Category

Documents

-

view

215 -

download

0

description

Transcript of T1CDA

UNIVERSIDAD AUTONOMA DE BAJA CALIFORNIA

MateriaCircuitos Digitales II

Ejercicios para Examen

Profesora:Ing. Teresa Carrillo

Circuitos Digitales II

Ejercicio 1:

Diseñe un circuito como red iterativa y como red secuencial, donde la salida Z = 1 sí al menos una de sus entradas X = 1 y no este en grupos de dos o más unos consecutivos.

Solucion: (Red Iterativa)

1.1 Diagrama de Estados.

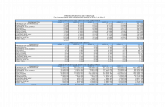

1.2 Tabla de Estados:Estado E. Próximo Presente 0 1 Salida

So S1 S2 S3

1.3 Tabla de transiciones:Estado E. Próximo Presente 0 1 Salida

OO O1 111

T.Carrillo 1

Z = 0

So

Z = 0

S3

Z = 1

S1

Z = 1

S2

{0,1}

0

0

0

1

11

Circuitos Digitales II

1O

1.4 Mapas de Karnaugh.0 1 0 1

OO OO 0 1O1 O1 0 11 11 1 10 10

1.5 Diagrama.

T.Carrillo 2

Circuitos Digitales II

Solucion: (Red Secuencial)

1.1 Diagrama de Estados.

1.2 Tabla de Estados:

Estado E. Próximo Presente 0 1 Salida

So S1 S2 S3

1.3 Tabla de transiciones:

Estado E. Próximo Presente 0 1 JA KA JB KB JA KA JB KB Salida

OO O1 11 1O

T.Carrillo 3

Z = 0

So

Z = 0

S3

Z = 1

S1

Z = 1

S2

{0,1}

0

0

0

1

11

Circuitos Digitales II

1.4 Mapas de Karnaugh.

0 1 0 1 0 1 0 1OO OO 0 1 OO OO O1 O1 0 O1 O1 11 11 1 11 11 1O 1O 1º 1O

1.5 Diagrama.

T.Carrillo 4

Circuitos Digitales II

2

La salida Z cambiara de valor al ocurrir el segundo uno dentro de un grupo se 1’s. Diseñar como red secuencial usando FF’S JK.

Solucion:

2.1 Diagrama de Estados.

2.2 Tabla de Estados.

Estado E. Próximo Presente 0 1 SalidaSo S1 S2 S3 S4

T.Carrillo 5

Z = 0

So

Z = 1

S3

Z = 0

S1Z = 1

S2

0

0

1

1 1 0

Z = 0

S4

0

0

1

1

Circuitos Digitales II

2.3 Tabla de Transiciones:

Estado E. Próximo Presente 0 1 JA KA JB KB JC KC JA KA JB KB JC KC SalidaOOO OO1 O1O O11 1OO 1O1 xxx xxx xxx xxx xxx xxx Xxx xxx xxx xxx xxx xxx xxx xxx x110 xxx xxx xxx xxx xxx xxx Xxx xxx xxx xxx xxx xxx xxx xxx x111 xxx xxx xxx xxx xxx xxx Xxx xxx xxx xxx xxx xxx xxx xxx x

2.4 Mapas de Karnaugh.

OO O1 111O OO O1 111O OO O1 111OOO OO OO O1 O1 O1 11 11 11 1O 1O 1O

OO O1 11 1O OO O1 111O OO O1 11 1OOO OO OOO1 O1 O111 11 111O 1O 1O

0 100011110

T.Carrillo 6

Circuitos Digitales II

2.5 Diagrama.

T.Carrillo 7

Circuitos Digitales II

3

Realice el diagrama y la tabla de estados, asi como la tabla de transiciones de un circuito detector de la siguiente secuencia:

X=01101111011Z=00111001110

Solucion:

3.1 Diagrama de estados.

3.2 Tabla de Estados.

Estado E. Próximo Presente 0 1 SalidaSo S1 S2 S3

3.3 Tabla de Transiciones.

Estado E. Próximo Presente 0 1 JA KA JB KB JA KA JB KB SALIDA

00 01 11 10

T.Carrillo 8

Z = 0

S1

Z = 0

So

Z = 1

S2

Z = 1

S3

00

0

0

11

1

1

Circuitos Digitales II

3.4 Mapas de Karnaugh.

0 1 0 1 0 1 0 1OO OO OO OO O1 O1 O1 O1 11 11 11 11 10 10 1O 10

0 10 1

3.5 Diagrama.

4T.Carrillo 9

Circuitos Digitales II

Diseñar un circuito secuencial sincrono (con FF’S D) con una entrada X y una salida Z,que reconosca la secuencia de entrada 01.

Solucion:

4.1 Diagrama de Estados.

4.2 Tabla de Estados.

Estado E. Próximo Presente 0 1 SalidaSo S1 S2

4.3 Tabla de Transiciones:

Estado E. PróximoPresente 0 1 DA DB DA DB Salida

00 01 11 10 XX XX X X X X X

4.4 Mapas de Karnaugh.

T.Carrillo 10

Z = 0

So

Z = 0

S1

Z = 1

S2

0

0

0

1

1

1

Circuitos Digitales II

0 1 0 1OO OO 0 1O1 O1 0 11 11 1 10 1O

4.5 Diagrama.

T.Carrillo 11

Circuitos Digitales II

5

Diseñar un circuito secuencial sincrono con FF’s T, con una linea de entrada y una de salida que reconozca la cadena de entrada X = 1111. Debe reconocer las secuencias traslapadas.

Solucion:

5.1 Diagrama de Estados.

5.2 Tabla de Estados.

EstadoE.

Próximo Presente 0 1 SalidaSo S1 S2 S3 S4

T.Carrillo 12

Z = 0

So

Z = 1

S3

Z = 0

S1

Z = 1

S2

0

0

0

1 1

1

Z = 0

S4

0

0

1 1

Circuitos Digitales II

5.3 Tabla de Transiciones.

EstadoE.

Próximo Presente 0 1 TA TB TC TA TB TC Salida000 001 010 011 100 xxx xxx xxx x x x x X x xxxx xxx xxx x x x x X x xxxx xxx xxx x x x x X x x

5.4 Mapas de Karnaugh.

OO O1 11 10 OO O1 11 10 OO O1 11 10 0 1OO OO OO 0 O1 O1 O1 1 11 11 11 11 10 1O 1O 10

5.5 Diagrama.

6

T.Carrillo 13

Circuitos Digitales II

6(me) Diseñar un circuito secuecial que reconosca la secuencia de entrada que consta de dos ceros seguidos por 10 (0010). Reconoce secuencias traslapadas.

Solucion:

6.1 Diagrama de Estados

T.Carrillo 14

Z = 0

So

Z =0

S5

0

Z = 0

S3

1

Z = 0

S1

Z = 0

S2

0

Z = 1

S4

0

00

1

1

1 0

1

1

Circuitos Digitales II

6.2 Tabla de Estados.

Estado E. Próximo Presente 0 1 SalidaSo S1 S0 0 S1 S2 S1 0 S2 S2 S3 0 S3 S4 S0 0 S4 S5 S0 1 S5 S5 S3 0

6.3 Tabla de Transiciones.

Estado E. Próximo X=0 X=1Presente 0 1 TA TB TC TA TB TC Salida000 001 000 0 0 1 0 0 0 0 001 010 001 0 0 1 0 0 0 0 010 010 011 0 0 0 0 0 1 0 011 100 000 1 1 1 0 1 1 0 100 101 000 0 0 1 1 0 0 1 101 101 011 0 0 0 1 1 0 0110 xxx xxx x x x x x X x111 xxx xxx x x x x x X x

6.4 Mapas de Karnaugh.

OO O1 11 10 CX OO O1 11 10 OO O1 11 10 0 1OO 0 0 0 0 OO 0 0 0 0 OO 1 0 0 1 o0 0 0O1 0 0 0 1 O1 0 0 1 1 O1 0 1 1 1 01 0 0 11 X X x x 11 x x x x 11 X x x x 11 X x1º 0 1 1 0 1O 0 0 1 0 1O 1 0 0 0 10 1 0

AB

Ax+bcx’ bc+acx b’c’x’+bx+a’cx’ ac’

6.5 Diagramas.

T.Carrillo 15

Circuitos Digitales II

T.Carrillo 16

Circuitos Digitales II

NOMBRE:__________________________________________________________________

INSTRUCCIONES: Resuelve los siguientes problemas incluyendo todo el procedimiento.

2 puntos extras: Quienes ganaron el OSCAR al mejor actor y a la mejor actriz este año.

1. Diseña un circuito secuencial sincrono con FF’s T, como máquina de estados Moore que reconozca la cadena de entrada X = 111. Debe reconocer las secuencias traslapadas.

Ejemplo: x = 1101111111010 z = 0000011111000

2. Diseña el detector de secuencias anterior pero como Red Iterativa.la celda inicial deberá ser simplificada.

X1 X2 X3

T.Carrillo 17

A Z 1 2 3 Red

salida

a1 a2 a3 an