diseno_de_circuitos_digitales_con_vhdl_v1.01

-

Upload

luis-fernando-hernandez -

Category

Documents

-

view

392 -

download

0

Transcript of diseno_de_circuitos_digitales_con_vhdl_v1.01

DiseodecircuitosdigitalesconVHDL FelipeMachado,SusanaBorromeo Versin1.01creadael20dejuliode2010 EstaversindigitaldeDiseodecircuitosdigitalesconVHDLhasidocreadaylicenciada porFelipeMachadoSnchezySusanaBorromeoLpezconunalicenciadeCreative Commons.Estalicenciapermitelosusosnocomercialesdeestaobraentantoencuantose atribuyaautoraoriginal.Estalicencianopermitealterar,transformarogenerarunaobra derivadaapartirdeestaobra Conestalicenciaereslibredecopiar,distribuirycomunicarpblicamente estaobrabajolascondicionessiguientes: Reconocimiento:debesreconocerycitaralosautoresdeestaobra Nocomercial:nopuedesutilizarestaobraparafinescomerciales Sinobrasderivadas:Nosepuedealterar,transformarogeneraruna obraderivadaapartirdeestaobra Paramsinformacinsobrelalicencia,visitaelsiguienteenlace: http://creativecommons.org/licenses/byncnd/3.0/ EstaobraestdisponibleenelarchivoabiertodelaUniversidadReyJuanCarlos: http://eciencia.urjc.es/dspace/handle/10115/4045 http://hdl.handle.net/10115/4045 Paramsinformacinsobrelosautores: http://gtebim.es/~fmachado http://gtebim.es/

ISBN:9788469346525

Diseo de circuitos digitales con VHDLVersin1.01creadael20dejuliode2010 FelipeMachadoSnchez SusanaBorromeoLpez DepartamentodeTecnologaElectrnica UniversidadReyJuanCarlos Mstoles,Madrid,Espaa http://gtebim.es/ http://gtebim.es/~fmachado

AmihermanoAle FMS

DiseodecircuitosdigitalesconVHDL

Agradecimientos QueremosagradeceralDepartamentodeTecnologaElectrnicadelaUniversidadReyJuanCarlos porfomentarladocenciadecalidadysuapoyoconstanteennuestraslaboresdocentes. Tambin queremos agradecer a los alumnos de Ingeniera de Telecomunicacin por su inters generalizadoenaprenderysuscomentariossobrenuestradocenciayprcticas LosAutores

DiseodecircuitosdigitalesconVHDL

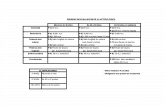

ndicendice............................................................................................................................................................ 1 Lista de acrnimos ....................................................................................................................................... 5 ndice de figuras ........................................................................................................................................... 6 ndice de cdigo VHDL................................................................................................................................. 9 ndice de tablas .......................................................................................................................................... 11 1. Introduccin ............................................................................................................................................ 13 2. Encender un LED ................................................................................................................................... 152.1. Tarjetas Pegasus y Basys..................................................................................................................................... 15 2.1.1. La tarjeta Pegasus ....................................................................................................................................... 15 2.1.2. La tarjeta Basys ........................................................................................................................................... 16 2.2. Cmo encender un LED........................................................................................................................................ 17 2.3. Diseo del circuito ................................................................................................................................................. 18 2.4. Sntesis e implementacin del circuito .................................................................................................................. 24 2.5. Programacin de la FPGA .................................................................................................................................... 26 2.5.1. Programacin de la tarjeta Pegasus............................................................................................................ 26 2.5.2. Programacin de la tarjeta Basys ................................................................................................................ 29 2.6. Cambiar el tipo de FPGA de un proyecto.............................................................................................................. 31 2.7. Trabajar desde varios ordenadores con un mismo proyecto ................................................................................ 32 2.8. Conclusin............................................................................................................................................................. 33

3. Sentencias concurrentes ........................................................................................................................ 343.1. Diseo de un multiplexor....................................................................................................................................... 35 3.1.1. Diseo usando puertas lgicas.................................................................................................................... 35 3.1.2. Diseo usando varias sentencias concurrentes .......................................................................................... 36 3.1.3. Uso de sentencias condicionales................................................................................................................. 37 3.1.4. Uso de procesos .......................................................................................................................................... 37 3.2. Diseo de un multiplexor de 4 alternativas ........................................................................................................... 38 3.3. Diseo de un multiplexor de 4 bits de dato y dos alternativas .............................................................................. 39 3.4. Conclusiones......................................................................................................................................................... 40

4. Codificadores, decodificadores, convertidores de cdigo....................................................................... 414.1. Convertidor de binario a 7 segmentos .................................................................................................................. 41 4.2. Decodificador de 2 a 4 .......................................................................................................................................... 43 4.3. Codificador de 8 a 3 .............................................................................................................................................. 45 4.4. Conclusiones......................................................................................................................................................... 48

5. Elementos de memoria........................................................................................................................... 505.1. Biestable J-K ......................................................................................................................................................... 50 5.2. Descripcin de biestables en VHDL para sntesis ................................................................................................ 51 5.3. Encendido y apagado de LED con un pulsador .................................................................................................... 54 5.3.1. Primera solucin .......................................................................................................................................... 55 5.3.2. Detector de flanco........................................................................................................................................ 55 5.4. Conclusiones......................................................................................................................................................... 59

6. Contadores ............................................................................................................................................. 616.1. Segundero............................................................................................................................................................. 61 6.2. Contador de 10 segundos ..................................................................................................................................... 63 6.3. Cronmetro ........................................................................................................................................................... 65 6.3.1. Mostrar los dgitos. Solucin manual ........................................................................................................... 67 6.3.2. Mostrar los dgitos. Solucin automtica ..................................................................................................... 68 6.3.3. Mejoras del circuito ...................................................................................................................................... 70 6.3.4. Optimizacin ................................................................................................................................................ 70 6.4. Contador manual................................................................................................................................................... 71 6.5. Conclusiones......................................................................................................................................................... 72

7. Registros de desplazamiento ................................................................................................................. 737.1. Registro de desplazamiento con carga paralelo ................................................................................................... 73 7.2. Rotacin a la derecha y a la izquierda .................................................................................................................. 75 7.3. Rotacin automtica.............................................................................................................................................. 76 7.3.1. Variantes del circuito.................................................................................................................................... 76 7.4. Conclusiones......................................................................................................................................................... 76

8. Simulacin .............................................................................................................................................. 778.1. Ejemplo sencillo .................................................................................................................................................... 78 8.2. Ampliacin............................................................................................................................................................. 86 8.3. Conclusiones......................................................................................................................................................... 86

9. Mquinas de estados finitos ................................................................................................................... 879.1. Mquina de estados para encender y apagar un LED con pulsador .................................................................... 87

Departamento de Tecnologa Electrnica

1

Diseo de circuitos digitales con VHDL - v1.01 - 20/07/10

9.1.1. Proceso combinacional que obtiene el estado siguiente ............................................................................. 89 9.1.2. Proceso secuencial...................................................................................................................................... 89 9.1.3. Proceso combinacional que proporciona las salidas ................................................................................... 89 9.2. Detector de flanco con mquinas de estados ....................................................................................................... 90 9.2.1. Variante........................................................................................................................................................ 91 9.3. Desplazamiento alternativo de los LED ................................................................................................................ 91 9.4. Conclusiones......................................................................................................................................................... 93

10. Clave electrnica .................................................................................................................................. 9510.1. Variantes ............................................................................................................................................................. 96

11. Circuito antirrebotes ............................................................................................................................. 97 12. Mquina expendedora .......................................................................................................................... 9912.1. Versin sencilla ................................................................................................................................................... 99 12.2. Versin decimal................................................................................................................................................. 100

13. Control con PWM ............................................................................................................................... 10113.1. Funcionamiento del PWM ................................................................................................................................. 101 13.2. Control de la intensidad de un LED................................................................................................................... 101 13.3. Ampliacin a control de motores ....................................................................................................................... 102

Circuitos digitales y analgicos................................................................................................................. 103 14. Control de motor paso a paso ............................................................................................................ 10514.1. Motores paso a paso......................................................................................................................................... 105 14.1.1. Identificacin de terminales ..................................................................................................................... 105 14.1.2. Secuencia del motor paso a paso............................................................................................................ 107 14.2. Generacin de la secuencia de control con la FPGA........................................................................................ 108 14.3. Circuito de potencia para gobernar el motor ..................................................................................................... 109 14.4. Conclusiones..................................................................................................................................................... 111

15. Piano electrnico ................................................................................................................................ 11315.1. Ampliaciones ..................................................................................................................................................... 114

Problemas tericos................................................................................................................................... 115 16. Reproductor MP3 ............................................................................................................................... 11716.1. Enunciado ......................................................................................................................................................... 117 16.2. Solucin............................................................................................................................................................. 118 16.2.1. Bloques internos del circuito .................................................................................................................... 118 16.2.2. Diagrama de transicin de estados ......................................................................................................... 118 16.2.3. Tabla de estados siguientes y salidas ..................................................................................................... 121 16.2.4. Tabla de excitacin de los biestables para biestables J-K ...................................................................... 122 16.2.5. Ecuacin simplificada para la salida Play ................................................................................................ 123 16.2.6. Modelo VHDL........................................................................................................................................... 123 16.3. Solucin alternativa ........................................................................................................................................... 125

17. Visualizacin del reproductor MP3 ..................................................................................................... 12917.1. Enunciado ......................................................................................................................................................... 129 17.2. Solucin............................................................................................................................................................. 130 17.2.1. Esquema interno del circuito.................................................................................................................... 130 17.2.2. Modelo en VHDL...................................................................................................................................... 130

18. Robot rastreador................................................................................................................................. 13318.1. Enunciado ......................................................................................................................................................... 133 18.2. Solucin............................................................................................................................................................. 135 18.2.1. Entradas, salidas y estados. Diagrama de estados................................................................................. 135 18.2.2. Tabla de estados siguientes y salidas ..................................................................................................... 137 18.2.3. Tabla de excitacin de biestables para biestables J-K ............................................................................ 138 18.2.4. Ecuaciones simplificadas......................................................................................................................... 139

19. Teclado de telfono mvil................................................................................................................... 14119.1. Enunciado ......................................................................................................................................................... 141 19.2. Solucin............................................................................................................................................................. 143 19.2.1. Bloques internos del circuito .................................................................................................................... 143 19.2.2. Diagrama de estados............................................................................................................................... 143

20. Clculo de temporizacin de un circuito 1 .......................................................................................... 14920.1. Enunciado ......................................................................................................................................................... 149 20.2. Solucin............................................................................................................................................................. 149 20.2.1. Metaestabilidad........................................................................................................................................ 149 20.2.2. Frecuencia mxima.................................................................................................................................. 149

21. Anlisis de un circuito 1 ...................................................................................................................... 15121.1. Enunciado ......................................................................................................................................................... 151 21.2. Solucin............................................................................................................................................................. 151 21.2.1. Tabla de excitacin del autmata ............................................................................................................ 151 21.2.2. Diagrama de transicin de estados ......................................................................................................... 152

22. Clculo de temporizacin de un circuito 2 .......................................................................................... 15322.1. Enunciado ......................................................................................................................................................... 153 22.2. Solucin............................................................................................................................................................. 153

2

Universidad Rey Juan Carlos

23. 24. Anlisis de un circuito 2 ................................................................................................................ 15524.1. Enunciado ......................................................................................................................................................... 155 24.2. Solucin............................................................................................................................................................. 155 24.2.1. Tabla de excitacin del autmata ............................................................................................................ 155 24.2.2. Diagrama de transicin de estados ......................................................................................................... 156

Referencias .............................................................................................................................................. 157

Departamento de Tecnologa Electrnica

3

Departamento de Tecnologa Electrnica

Lista de acrnimosALU CAD CPLD DTE ED1 ED2 ETSIT FPGA FSM IEEE LED LSB MSB PWM URJC UUT VHDL VHSIC ArithmeticLogicUnit UnidadAritmticoLgica ComputerAidedDesgin Diseoasistidoporordenador ComplexProgrammableLogicDevice Dispositivodelgicaprogramablecomplejo DepartamentodeTecnologaElectrnica ElectrnicaDigitalI AsignaturadelatitulacindeIngenieradeTelecomunicacindelaURJC ElectrnicaDigitalII AsignaturadelatitulacindeIngenieradeTelecomunicacindelaURJC EscuelaTcnicaSuperiordeIngenieradeTelecomunicacin EscueladelaUniversidadReyJuanCarlos FieldProgramableGateArray Dispositivodelgicaprogramable,demayoresprestacionesquelosCPLD FiniteStateMachine Mquinadeestadosfinitos InstituteofElectricalandElectronicsEngineers InstitutodeIngenierosElctricosyElectrnicos LightEmittingDiode Diodoemisordeluz LeastSignificantBit Bitmenossignificativo MostSignificantBit Bitmssignificativo PulseWidthModulation Modulacinporanchodepulso UniversidadReyJuanCarlos UniversidadpblicadeMadrid,Espaa UnitUnderTest Unidadbajoprueba VHSICHardwareDescriptionLanguage Untipodelenguajededescripcindehardware VeryHighSpeedIntegratedCircuit Circuitointegradodemuyaltavelocidad

Departamento de Tecnologa Electrnica

5

Departamento de Tecnologa Electrnica

ndice de figurasFigura2.1:PlacaPegasusdeDigilent ................................................................................................................................................... 16 Figura2.2:PlacaBasysdeDigilent ....................................................................................................................................................... 17 Figura2.3:ConexindelosLEDdelaplacaPegasus(izquierda)ylaBasys(derecha) .............................................................. 17 Figura2.4:Ventanaparalacreacindenuevoproyecto .................................................................................................................. 19 Figura2.5:InterpretacindeltextodelencapsuladodelaFPGAdelaPegasus .......................................................................... 19 Figura2.6:InterpretacindeltextodelencapsuladodelaFPGAdelaBasys............................................................................... 19 Figura2.7:Ventanaparalaseleccindeldispositivodelnuevoproyecto..................................................................................... 20 Figura2.8:Seleccindeltipodelanuevafuentequevamosacrear .............................................................................................. 20 Figura2.9:Definicindelospuertos .................................................................................................................................................... 21 Figura2.10:Aparienciadelaherramientaalaadirlanuevafuenteled0.vhd............................................................................. 21 Figura2.11:AparienciadelaherramientaparaempezararealizarladescripcinVHDL......................................................... 22 Figura2.12:Cajanegraquedefinelaentidaddenuestrocircuito................................................................................................ 23 Figura2.13:Seleccinparalaasignacindepines ............................................................................................................................. 24 Figura2.14:HerramientaPACEparalaasignacindepines........................................................................................................... 25 Figura2.15:Aspectodelasubventanadeprocesosunavezquesehasintetizadoeimplementadoeldiseo correctamente.Enlaventanadeladerecha,enelprocesodesntesishahabidoadvertencias(warnings) quenosiempresonimportantes,yporesotieneunsmbolotriangulardecoloramarillo .................................. 26 Figura2.16:Jumpersysuconexin ...................................................................................................................................................... 26 Figura2.17:iMPACT:componentesdetectadosyasignacindeunficherodeconfiguracin.................................................. 27 Figura2.18:OrdenparaprogramarlaFPGA...................................................................................................................................... 28 Figura2.19:Programacinrealizadaconxito ................................................................................................................................... 29 Figura2.20:PantallainicialdelAdept,sindispositivosconectados ............................................................................................... 30 Figura2.21:PantalladelAdeptquehadetectadoalgndispositivosconectado ......................................................................... 30 Figura2.22:PantalladelAdeptquehadetectadolacadenaJTAGdedispositivos(FPGAyPROM) ...................................... 31 Figura2.23:ProcedimientoparacambiarlascaractersticasdelaFPGA....................................................................................... 32 Figura3.1:EsquemaelctricodelasconexionesdelosinterruptoresypulsadoresenlaplacaPegasus ................................. 34 Figura3.2:EsquemaelctricodelasconexionesdelosinterruptoresypulsadoresenlaplacaBasys ..................................... 34 Figura3.3:ListadepalabrasreservadasdelVHDL........................................................................................................................... 35 Figura3.4:Esquemadelmultiplexor(izquierda)ydiseoenpuertas(derecha) ......................................................................... 35 Figura3.5:Esquemaenpuertasdelmultiplexorconsealesintermedias..................................................................................... 36 Figura3.6:Multiplexorde4alternativas ............................................................................................................................................. 38 Figura3.7:Definicindelospuertosdeentradaysuancho............................................................................................................ 38 Figura3.8:Multiplexorde4bitsdedato ............................................................................................................................................. 39 Figura4.1:Multiplexorysalidaa7segmentos................................................................................................................................... 41 Figura4.2:Los16nmerosrepresentablescon4bits ........................................................................................................................ 42 Figura4.3:Valoresdelvectordelossegmentos(SEG)paralosnmeros0,1y2......................................................................... 42 Figura4.4:Sentenciasconcurrentesdelaarquitectura...................................................................................................................... 43 Figura4.5:Puertosdeldecodificadorytabladeverdad................................................................................................................... 44 Figura4.6:Esquemadelcircuitodeldecodificadorcompleto.......................................................................................................... 44 Figura4.7:Esquemaytabladeverdaddelcodificadorde8a3 ...................................................................................................... 46 Figura4.8:Esquemadebloquesdelcodificador ................................................................................................................................ 46 Figura4.9:SentenciasVHDLdelesquemadelafigura4.8 .............................................................................................................. 47 Figura5.1:TabladeverdaddelbiestableJK(izquierda)ycircuitoquequeremosimplementar(derecha) ........................... 50 Figura5.2:EditorderestriccionesdelISE(XilinxConstraintsEditor) ........................................................................................... 51 Figura5.3:TabladeverdaddelbiestableTysuesquema................................................................................................................ 55 Figura5.4:Cronogramaresultantedepulsarelbotndeencendido/apagado ............................................................................ 56 Figura5.5:Circuitodetectordeflancosinregistrarlaentrada(Mealy:norecomendadoparaestecaso) ............................... 56 Figura5.6:CronogramadeldetectordeflancorealizadoporMealy(norecomendadoparaestecaso) .................................. 57 Figura5.7:Circuitodetectordeflancoregistrandolaentrada(Moore:recomendadoparaestecaso) ..................................... 57 Figura5.8:CronogramadeldetectordeflancorealizadoporMoore(recomendadoparaestecaso) ....................................... 57 Figura5.9:CircuitoqueenciendeyapagaunLEDconelmismopulsador .................................................................................. 58 Figura5.10:CdigoVHDLdelcircuitocompleto .............................................................................................................................. 58 Figura6.1:Cronogramadelasealquequeremosobtener.............................................................................................................. 61 Figura6.2:Esquemadelcircuitoquequeremosrealizar................................................................................................................... 61 Figura6.3:Esquemadelcontadorde10segundos ............................................................................................................................ 63 Figura6.4:Entradasysalidasdelcircuito ........................................................................................................................................... 65 Figura6.5:Cronogramadelasealdeunadcimadesegundoquequeremosobtener............................................................. 65 Figura6.6:Esquemadelcronmetro .................................................................................................................................................... 66

Departamento de Tecnologa Electrnica

6

ndice de figuras

Figura6.7:Esquemadelprocesocontadordedcimas ..................................................................................................................... 66 Figura6.8:Codificadorparacontrolarlosnodosdelosdisplays.................................................................................................. 67 Figura6.9:MultiplexorqueseleccionalacifraBCDsegnlaconfiguracindeosinterruptores.............................................. 67 Figura6.10:Esquemacompletodelcronmetroconvisualizacinmanual ................................................................................... 68 Figura6.11:Cronogramadelasealdeunamilsimadesegundoquequeremosobtener ...................................................... 68 Figura6.12:Multiplexadoeneltiempoparamostrarlosdisplays .................................................................................................. 69 Figura6.13:Esquemacompletodelcronmetroconvisualizacinautomtica............................................................................. 70 Figura6.14:Otraalternativaalesquemadelafigura6.9 ................................................................................................................... 71 Figura6.15:Diagramadeestadosdelcontadorascendente/descendentequevamosarealizar ............................................... 71 Figura6.16:Esquemadelcontadorqueimplementaremos.............................................................................................................. 72 Figura7.1:Esquemadelregistrodedesplazamientoalaizquierdaconcargaparalelo ............................................................. 73 Figura7.2:Desplazamientoalaizquierda........................................................................................................................................... 74 Figura7.3:Rotacinalaizquierda........................................................................................................................................................ 75 Figura7.4:Esquemadelcircuitoderotacinautomtica ................................................................................................................. 76 Figura8.1:Esquemageneraldeunbancodepruebas....................................................................................................................... 78 Figura8.2:Puertosdeentradaysalidadelcontadorquevamosaprobar .................................................................................... 78 Figura8.3:SeleccindenuevafuentedetipoVHDLTestBench.................................................................................................... 79 Figura8.4:CdigocreadoautomticamenteporelISEparaelbancodepruebas....................................................................... 80 Figura8.5:Distintaspartesdelareferencia(instanciacin)auncomponente........................................................................... 81 Figura8.6:Periododelasealdereloj................................................................................................................................................. 81 Figura8.7:Seleccindelentronoparasimulacin ............................................................................................................................. 82 Figura8.8:Entronoparasimulacin..................................................................................................................................................... 83 Figura8.9:Cambiodelaspropiedadesdelproyecto......................................................................................................................... 84 Figura8.10:SeleccindelISESimulator .............................................................................................................................................. 84 Figura8.11:Arranquedelasimulacin ............................................................................................................................................... 85 Figura8.12:Resultadodelasimulacin............................................................................................................................................... 85 Figura8.13:Visualizacindecuentacomodecimalsinsigno....................................................................................................... 86 Figura9.1:Esquemageneraldelosprocesosdeunamquinadeestados .................................................................................... 87 Figura9.2:BloquesdelcircuitoparaencenderyapagarunLED.................................................................................................... 88 Figura9.3:DiagramadetransicindeestadosparaencenderunLEDconunpulsador............................................................ 88 Figura9.4:Diagramadeestadosdeldetectordeflancos(Moore)................................................................................................... 90 Figura9.5:Cronogramadecuandollegalasecuencia0101.............................................................................................................. 91 Figura9.6:Diagramadeestadosmodificado ...................................................................................................................................... 91 Figura9.7:EsquemadelcircuitodelmovimientoalternativodelosLED ..................................................................................... 92 Figura9.8:Diagramadetransicindeestados ................................................................................................................................... 93 Figura10.1:Esquemadelcircuitodelaclaveelectrnica ................................................................................................................. 96 Figura11.1:EsquemadelospulsadoresenlaplacaPegasusyenlaplacaBasys ........................................................................ 97 Figura11.2:Cronogramadelasalidadeldetectordeflancos(PULSO_BTN)cuandohayrebotesenlaentrada(BTN) ........ 97 Figura11.3:Cronogramadelasalidadelfiltroantirrebotes(FILTRO_BTN)cuandohayrebotesenlaentrada(BTN) ........ 98 Figura11.4:Esquemadelcircuitoquefiltralosrebotesdelaentrada............................................................................................ 98 Figura11.5:Diagramadeestadosdelcircuitoquefiltralospulsos ................................................................................................ 98 Figura12.1:Esquemadepuertosdeentradaysalidadelcontroldelamquinaexpendedora ................................................ 99 Figura12.2:Esquemainternodelcircuitodecontroldelamquinaexpendedorasimple ...................................................... 100 Figura12.3:Indicacionesdelosdisplayssegnelestado............................................................................................................... 100 Figura13.1:SealPWMqueselehacambiadoelciclodetrabajo................................................................................................ 101 Figura13.2:ControldevelocidadconelPWM ................................................................................................................................ 101 Figura13.3:Los8ciclosdetrabajoposiblesconunPWMde3bitsderesolucin..................................................................... 102 Figura13.4:CircuitodepotenciaparacontrolarelmotordesdelaFPGA................................................................................... 102 Figura14.1:Conexininternadeunmotorunipolar ...................................................................................................................... 106 Figura14.2:ElterminalAatierra ....................................................................................................................................................... 106 Figura14.3:Resultadodeponeratierracadaunodelosotrostresterminales,cuandoelmotorpierdeparindicaque eselcorrespondiente ....................................................................................................................................................... 106 Figura14.4:IdentificacindelosterminalesennuestromotorPM55L048deMinebea .......................................................... 107 Figura14.5:Secuenciadeterminalesqueseponenatierraparaobtenerelgirodelmotor ..................................................... 107 Figura14.6:Secuenciadeterminalesqueseponenatierraparaobtenerelgirodelmotorenambossentidos ................... 107 Figura14.7:BloquedecontroldemotordelaFPGA ...................................................................................................................... 108 Figura14.8:EsquemadelamquinadeestadosparaelbloquedecontroldemotordelaFPGA.......................................... 109 Figura14.9:Posibleesquemadelaelectrnicadepotenciaparamanejarelmotor ................................................................... 110 Figura14.10:Esquemadelcircuitoconoptoacopladores ............................................................................................................... 110 Figura14.11:EsquemadelcircuitousandoelcircuitointegradoSN754410.............................................................................. 111 Figura15.1:Esquemadelcircuitodepianoelectrnicobsico ...................................................................................................... 113 Figura15.2:Esquemageneraldelcircuitodeamplificacin .......................................................................................................... 114 Figura16.1:Bloquesinternosdelcircuito .......................................................................................................................................... 118 Figura16.2:Ordendeentradasysalidasenlarepresentacindelamquinadeestados........................................................ 119

Departamento de Tecnologa Electrnica

7

Diseo de circuitos digitales con VHDL - v1.01 - 20/07/10

Figura16.3:Estadoinicial..................................................................................................................................................................... 119 Figura16.4:Transicinaunestadodeespera .................................................................................................................................. 119 Figura16.5:Transicinaestadodereproduccinoavance ........................................................................................................... 120 Figura16.6:Estadodereproduccinyavance.................................................................................................................................. 120 Figura16.7:Transicindesdeelestadodeavancealestadodereproduccin........................................................................... 120 Figura16.8:Diagramafinaldelamquinadeestados.................................................................................................................... 121 Figura16.9:DiagramadeKarnaughyecuacindelasalidaPlay................................................................................................. 123 Figura16.10:Diagramadebloquesdelasolucinalternativa....................................................................................................... 125 Figura16.11:Diagramadebloquesmsdetalladodelasolucinalternativa............................................................................. 126 Figura16.12:Ordendeentradasysalidasenlarepresentacindelaprimeramquinadeestados ..................................... 126 Figura16.13:Diagramadelaprimeramquinadeestadosdelasolucinalternativa............................................................. 126 Figura16.14:Ordendeentradasysalidasenlarepresentacindelasegundamquinadeestados..................................... 127 Figura16.15:Diagramadelasegundamquinadeestadosdelasolucinalternativa............................................................ 127 Figura17.1:Textoquedebendemostrarlosdisplaysdesietesegmentos .................................................................................. 129 Figura17.2:Segmentosdeldisplay..................................................................................................................................................... 129 Figura17.3:Esquemadelcircuito ....................................................................................................................................................... 129 Figura17.4:Esquemadelcircuitodevisualizacin ......................................................................................................................... 130 Figura18.1:Cochevistodesdearriba................................................................................................................................................. 133 Figura18.2:Esquemadeentradasysalidasdelsistemadecontrol .............................................................................................. 133 Figura18.3:Distintasposicionesdelcocherespectoalalnea....................................................................................................... 134 Figura18.4:Posicindelosreceptoresrespectoalalneaygiro .................................................................................................. 135 Figura18.5:Ordendeentradasysalidaseneldiagramadeestados............................................................................................ 136 Figura18.6:Estadoinicialysustransiciones .................................................................................................................................... 136 Figura18.7:Estadosconundetectorsobrelalneayotrofuera.................................................................................................... 136 Figura18.8:Diagramadeestadosfinalsinreducir .......................................................................................................................... 137 Figura18.9:Diagramadeestadosfinalreducido ............................................................................................................................ 137 Figura18.10:MapasdeKarnaughyecuacionesdelasentradasdelosbiestables ..................................................................... 139 Figura19.1:Esquemadeentradasysalidasdelsistemadecontrol .............................................................................................. 141 Figura19.2:Bloquesinternosdelcircuito .......................................................................................................................................... 143 Figura19.3:Ordendeentradasysalidaseneldiagramadeestados............................................................................................ 143 Figura19.4:Ordendeentradasysalidaseneldiagramadeestados.Salidasconinicialesparasimplificar......................... 143 Figura19.5:Estadoinicial..................................................................................................................................................................... 143 Figura19.6:Estadodeespera............................................................................................................................................................... 144 Figura19.7:Estadodeesperaaquesueltelatecla ........................................................................................................................... 144 Figura19.8:Sefijaeldosenelcasoimprobablequesueltelateclaalavezqueterminalatemporizacin .......................... 145 Figura19.9:Sesueltalateclaantesdequepaseunsegundo:nuevaespera ............................................................................... 145 Figura19.10:NuevaesperaaquesesuelteB.................................................................................................................................... 146 Figura19.11:SehasoltadoPantesdequepaseunsegundo ......................................................................................................... 146 Figura19.12:EnlaesperaaversisevuelveapulsarPmostrandolaB....................................................................................... 147 Figura19.13:Diagramadeestadosfinal ............................................................................................................................................ 148 Figura20.1:Circuitoparaanalizar...................................................................................................................................................... 149 Figura21.1:Diagramadetransicindeestados ............................................................................................................................... 152 Figura22.1:Circuitoparaanalizar...................................................................................................................................................... 153 Figura24.1:Circuitoparaanalizar...................................................................................................................................................... 155 Figura24.2:Diagramadetransicindeestados ............................................................................................................................... 156

8

Universidad Rey Juan Carlos

ndice de cdigo VHDLCdigo21:ArquitecturaqueenciendeunLEDyapagaotro ......................................................................................................... 23 Cdigo31:Sentenciaconcurrentequedefineelmultiplexorenpuertas ...................................................................................... 36 Cdigo32:Sentenciasconcurrentesquedefinenelmultiplexorenpuertas(equivalentealcdigo31) ................................ 36 Cdigo33:Otraversindelassentenciasconcurrentesquedefinenelmultiplexorenpuertas(equivalentealos cdigos31y32) ................................................................................................................................................................ 37 Cdigo34:Sentenciaconcurrentecondicionadaquedefineelmultiplexor................................................................................. 37 Cdigo35:Sentenciaconcurrentecondicionadaquedefineelmultiplexor................................................................................. 37 Cdigo36:Entidaddelmultiplexorde4alternativas....................................................................................................................... 38 Cdigo37:Sentenciaconcurrentecondicionadaquedefineelmultiplexordecuatroalternativas ......................................... 39 Cdigo38:ProcesoconsentenciaIF ................................................................................................................................................... 39 Cdigo39:ProcesoconsentenciaCASE............................................................................................................................................... 39 Cdigo310:Entidaddelmultiplexorde4alternativas..................................................................................................................... 39 Cdigo41:Decodificadorconsentenciaconcurrente........................................................................................................................ 45 Cdigo42:Decodificadorconproceso................................................................................................................................................. 45 Cdigo43:Unaformadeasignarelmismovaloratodoslosbitsdeunvector........................................................................... 45 Cdigo44:Habilitacinconsealauxiliar......................................................................................................................................... 47 Cdigo45:Habilitacindentrodelasentencia ................................................................................................................................. 48 Cdigo46:Otraalternativaalcircuitodelafigura4.8,todoenunmismoproceso ................................................................... 48 Cdigo51:ProcesoqueimplementaunbiestableJK ...................................................................................................................... 50 Cdigo52:OtraalternativaparaelbiestableJK .............................................................................................................................. 50 Cdigo53:SentenciaderelojCORRECTA ........................................................................................................................................ 52 Cdigo54:sentenciaderelojINCORRECTA .................................................................................................................................... 52 Cdigo55:Inicializacinsncrona ....................................................................................................................................................... 52 Cdigo56:Asignacinantesdelainicializacin.INCORRECTA ................................................................................................. 52 Cdigo57:Asignacinfueradelreloj.INCORRECTA .................................................................................................................... 52 Cdigo58:Asignacindespusdelasentenciadereloj.INCORRECTA..................................................................................... 53 Cdigo59:Listadesensibilidadconelrelojylassealesasncronas ........................................................................................... 53 Cdigo510:Procesoequivalentealdelcdigo511 ......................................................................................................................... 53 Cdigo511:Procesoequivalentealdelcdigo510 ......................................................................................................................... 53 Cdigo512:Procesocombinacional(nogeneralatch).Correcto.................................................................................................... 54 Cdigo513:Procesoquegeneralatch.Posiblementenoloquierasgenerar ............................................................................... 54 Cdigo514:Procesocombinacional(nogeneralatch) ..................................................................................................................... 54 Cdigo515:Procesoqueesposiblequegenerelatch.Norecomendado...................................................................................... 54 Cdigo516:Procesocombinacionalequivalentealcdigo512(nogeneralatch)...................................................................... 54 Cdigo517:Procesocombinacionalequivalentealcdigo514(nogeneralatch)...................................................................... 54 Cdigo518:ProcesoqueimplementaunbiestableT ....................................................................................................................... 55 Cdigo519:AlternativaquedescribeelbiestableT ......................................................................................................................... 55 Cdigo520:Procesoqueimplementalos2biestablesD ................................................................................................................. 59 Cdigo521:Procesoequivalenteal520............................................................................................................................................. 59 Cdigo61:Arquitecturadelcontador................................................................................................................................................. 62 Cdigo62:Procesoequivalentealosdosprocesosdelcdigo61 ................................................................................................ 63 Cdigo63:Declaracindesealunsigned ...................................................................................................................................... 64 Cdigo64:BibliotecaspordefectoqueponeelISE .......................................................................................................................... 64 Cdigo65:Bibliotecasrecomendadas................................................................................................................................................. 64 Cdigo66:Procesoquecuenta10segundos...................................................................................................................................... 65 Cdigo67:Procesocontadordedcimas ........................................................................................................................................... 66 Cdigo68:Cdigodelcontadorascendente/descendentequenosedesborda........................................................................... 72 Cdigo71:Cdigodelprocesoderegistrodedesplazamiento...................................................................................................... 74 Cdigo72:Cdigoequivalentealcdigo71 .................................................................................................................................... 74 Cdigo73:Cdigoequivalentealcdigo71 .................................................................................................................................... 74 Cdigo74:Cdigodelprocesoquerotaaizquierdayderecha ..................................................................................................... 75 Cdigo75:Cdigoequivalentealcdigo74 .................................................................................................................................... 75 Cdigo81:CdigoquesimulaelfuncionamientodelrelojdelaplacaPegasus(50MHz)....................................................... 81 Cdigo82:Cdigoquesimulaelfuncionamientodelreset............................................................................................................ 82 Cdigo91:Declaracindeuntipoenumeradoparalamquinadeestados ............................................................................... 88 Cdigo92:Declaracindelassealesdeestadodetipoestados_led anteriormentedeclarado ....................................... 88 Cdigo93:Procesoqueobtieneelestadosiguiente ......................................................................................................................... 89 Cdigo94:Procesoqueactualizayguardaelestado....................................................................................................................... 89

Departamento de Tecnologa Electrnica

9

Diseo de circuitos digitales con VHDL - v1.01 - 20/07/10

Cdigo95:Procesoqueproporcionalasalida................................................................................................................................... 90 Cdigo96:Declaracindetiposenumeradosdistintosparacadamquinadeestados ............................................................ 90 Cdigo97:Cdigodelprocesocombinacionalqueobtieneelestadosiguiente ......................................................................... 93 Cdigo161:EntidaddelcircuitoMP3 .............................................................................................................................................. 123 Cdigo162:ArquitecturadelcircuitoMP3...................................................................................................................................... 125 Cdigo171:ArquitecturadelcircuitodevisualizacindelMP3 ................................................................................................. 131

10

Universidad Rey Juan Carlos

ndice de tablasTabla61:Displaysquesemuestransegnlaconfiguracindelosinterruptores....................................................................... 67 Tabla151:Frecuenciasdelasnotasendistintasoctavas ................................................................................................................ 113 Tabla16.1:Codificacindeestados .................................................................................................................................................... 121 Tabla16.2:Tabladeestadossiguientesysalidas ............................................................................................................................. 122 Tabla16.3:TabladeentradasnecesariasparaobtenerunatransicinenbiestablesJK ........................................................... 122 Tabla16.4:TabladeexcitacindelosnecesariasparaobtenerunatransicinenbiestablesJK ............................................ 123 Tabla18.1:Codificacindeestados .................................................................................................................................................... 137 Tabla18.2:Tabladeestadossiguientesysalidas ............................................................................................................................. 138 Tabla18.3:TabladeentradasnecesariasparaobtenerunatransicinenbiestablesJK ........................................................... 138 Tabla18.4:TabladeexcitacindelosnecesariasparaobtenerunatransicinenbiestablesJK ............................................ 139 Tabla20.1:Caractersticasdeloscomponentesdelcircuito ........................................................................................................... 149 Tabla20.2:Tiemposdepropagacinmximos ................................................................................................................................. 150 Tabla21.1:Tabladelestadosiguiente ................................................................................................................................................ 151 Tabla21.2:Tabladeexcitacindelautmata .................................................................................................................................... 151 Tabla22.1:Caractersticasdeloscomponentesdelcircuito ........................................................................................................... 153 Tabla22.2:Tiemposdepropagacinmximos ................................................................................................................................. 153 Tabla24.1:Tablasdeverdaddelasentradasdelosbiestables ...................................................................................................... 155 Tabla24.2:Tabladelestadosiguiente ................................................................................................................................................ 156 Tabla24.3:Tabladeexcitacindelautmata .................................................................................................................................... 156

Departamento de Tecnologa Electrnica

11

1. IntroduccinEstemanualesunaguaprcticaparaaprenderadisearcircuitosdigitalesmedianteel uso de VHDL y dispositivos lgicos programables (CPLD o FPGA). Este manual se ha desarrollado en el Departamento de Tecnologa Electrnica [5] de la Universidad Rey Juan Carlos para las prcticas de la asignatura Electrnica Digital II (ED2 [8]) de la titulacin de Ingeniera de Telecomunicacin1. Previamente, los alumnos de esta carrera hancursadolaasignaturaElectrnicaDigitalI(ED1).EnED1losalumnosadquirieronlos conceptos bsicos de la electrnica digital y realizaron diseos tanto con componentes discretoscomocondispositivoslgicosprogramables.LasprcticasrealizadasconFPGA deED1estnguiadasenelmanualdelareferencia[12].Endichasprcticasseenseaa disearcircuitoselectrnicosdigitalesconesquemticosyFPGA. Por tanto para seguir este manual con una mayor comprensin se recomienda tener conceptosbsicosdelossistemasdenumeracinyelectrnicadigital:diseoconpuertas lgicas,bloquescombinacionales,elementosdememoria,registrosycontadores.Realizar lasprcticasdeED1[12]esunabuenabaseparaseguirestemanual. Adems de las prcticas de clase, en este manual se han incluido dos secciones adicionales.Porunlado,apartirdelapgina103sehaaadidounaseccindecircuitos digitalesyanalgicosenlaqueseincluyendoscaptulosconalgunasindicacionessobre cmo realizar la parte analgica de los circuitos. Por otro lado, a partir de la 115 se ha incluidolaresolucindeproblemastericos.Estosproblemasfueronejerciciosdeexamen duranteelcurso20082009. Aspues,comoyasehadicho,enestemanualaprenderemosadisearcircuitosdigitales medianteVHDLyelusodedispositivoslgicosprogramables.ElVHDLesunlenguaje de descripcin de hardware que permite modelar y disear circuitos electrnicos digitales. Se pueden disear circuitos electrnicos digitales sin utilizar lenguajes de descripcindehardware.Porejemplo,usandoesquemticospodemosdisearuncircuito electrnico digital [12]. Disear mediante esquemticos es una manera ms intuitiva y menosabstractadedisear,yporestocreemosqueeslaformamsrecomendablepara aprender a disear. Si no tenemos unas bases slidas en el diseo con esquemticos, al disear con VHDL podemos perder la nocin de lo que estamos haciendo y pensar que estamosusandounlenguajedeprogramacinhabitual(C,Pascal,...).Notenerunaidea aproximadadelhardware(esquemtico)quesegeneraapartirdelcdigoVHDLesuna delaslimitacionesmsgrandesquepodemostenercomodiseadores. Sinembargo,unavezquesabemosdisearconesquemticos,loslenguajesdedescripcin dehardwarenosfacilitaneldiseoyaque,entreotrosbeneficios,nosproporcionan: Unniveldeabstraccinmayor,ahorrndonosmuchosdetallesdelaimplementacin Unamayorfacilidadparalareutilizacinyhacermodificaciones Unamayorcapacidadparamanejarparamanejarcircuitosgrandes

1

Esteplandeestudiosempezaextinguirseapartirdelcurso20092010conlaimplantacindelosgradosde Boloniaenelprimercurso

Departamento de Tecnologa Electrnica

13

Diseo de circuitos digitales con VHDL - v1.01 - 20/07/10

Posibilidadderealizarbancosdepruebasmscomplejosparasimularlafuncionalidad denuestrodiseo. Estos beneficios los podremos apreciar si comparamos el cdigo VHDL de los diseos propuestosconsudiseoenesquemticos.Porejemplo,podremoscompararelcontador realizadoconVHDL(captulo6) conelcontadorrealizadoenesquemticos(captulo19 delareferencia[12]). ElVHDLesunestndardelInstitutodeIngenierosElctricosyElectrnicos2(IEEE[13]). Existen otros lenguajes de descripcin de hardware como el Verilog o el SystemC. Histricamente,elusodeVHDLoVeriloghadivididoalacomunidaddediseadores,lo quehaprovocadodificultadesenelintercambiodediseosyalasempresasquefabrican herramientasinformticasdeayudaaldiseo(CAD). ElVHDLesunlenguajemuyamplioquefuecreadoparamodelarcircuitos.Mstardese empez a utilizar para disear circuitos, utilizando para ello slo un conjunto reducido del VHDL, lo que se llama VHDL para sntesis [14]. La transformacin de un circuito descrito en VHDL a su esquema en puertas lgicas y biestables se llama sntesis. Esta sntesislarealizanautomticamentelasherramientasCAD,graciasaestolosdiseadores ahorranmuchotiempodediseo.Enestemanualnoaprenderemosautilizarlatotalidad del VHDL, sino que usaremos un conjunto restringido del lenguaje orientado a sntesis. Lo que es ms, tampoco usaremos todo el conjunto de VHDL para sntesis, sino que utilizaremosloquevayamosnecesitando.Porsuerteopordesgracia,enVHDLunacosa se puede describir de muchas maneras distintas. Por lo general, en este manual aprenderemosslounadeellas. Por ltimo, con el fin de que este manual pueda llegar al mayor nmero de personas y conelobjetivodegenerarmaterialeducativoabierto,hemospublicadoestemanualbajo licenciaCreativeCommons[3]quepermitecopiarloydistribuirlo.Esperamosquedisfrutes desulecturayqueteayudeaaprenderadisearcircuitoselectrnicosdigitales.Parair mejorando el manual, agradeceremos la comunicacin de comentarios, sugerencias y correccionesalasdireccionesdecorreoelectrnicodelosautores. [email protected]@urjc.es.

2

InstituteofElectricalandElectronicsEngineers

14

Universidad Rey Juan Carlos

2. Encender un LEDEnlasprcticasdeestemanualrealizaremosdiseosbastantemscomplejosquelosque hicimosenElectrnicaDigitalI[12].Porunladoporqueyasabemosmsdeelectrnicay porotroladoporquedisearemosconVHDL.ElVHDLesunlenguajededescripcinde hardwarequenospermitirrealizardiseosavanzadosdemaneramsrpidayeficiente quecuandousbamoslosesquemticos. Como ya vimos en las prcticas de Electrnica Digital I, siempre que se introduzca una novedadeneldiseodebemosrealizarundiseodepruebalomssencilloposiblepara ver si todo funciona bien. En nuestro caso, en esta primera prctica queremos probar el proceso de diseo en VHDL, as que vamos a realizar un diseo VHDL que sea muy sencilloparaprobarquetodoloprocesovabien.Portanto,nuestrodiseodepruebaser encenderunLEDdescribiendoelcircuitoenVHDLenvezdeenesquemticos. EstaprcticanosservirpararepasarelentornodediseodeXilinx[25]:elISEWebPack3 [15].Enelrestodelasprcticasnoseharreferenciaalentornodedesarrollo.Asquesi tienesdudasdecmoimplementarelcircuitoenlaFPGA,vuelveaestaprcticaorepasa lasprcticasdelaopasado[12].

2.1. Tarjetas Pegasus y BasysLatarjetaqueutilizaremosenprcticaseslaPegasus[19]delaempresaDigilent[6].Esta tarjetayanoseproduce,perosepodrutilizarsinmuchadificultadcualquierotrotipode placasquetengancaractersticassimilares,comolaBasys[2]olaNexys,... Como hay algunas diferencias en la programacin de la Pegasus y la Basys, en los siguientessubapartadosseexplicarncadaunadeellas. 2.1.1. La tarjeta Pegasus LatarjetaPegasuscontieneunaFPGAdeXilinxdemodeloSpartanIIXC2S50XC2S200 con encapsulado PQ208. Estas FPGA tienen respectivamente 50000 200000 puertas lgicasequivalentesy140pinesdisponiblesparaelusuario.Conestacapacidadpodemos hacerdiseosdigitalesbastantegrandes. LaplacaPegasuscontienedistintosperifricosquenosfacilitarnlatareadeldiseo,como porejemplo:8LED,4displaysde7segmentos,4botones,8interruptores,unpuertoPS/2 (para ratn o teclado), un puerto VGA (para conectar un monitor), y varios puertos de expansin.Enlafigura2.1semuestralaplacaPegasus,yenlaquesesealanvariosdesus componentes.Lafotodelaplacanocoincideexactamenteconlaversindelaplacaque tenemos en el laboratorio y hay algunos componentes que no estn en el mismo lugar, aunquestodoslosquesehansealado.

3

Herramientagratuitaquesepuededescargaren: http://www.xilinx.com/webpack/classics/wpclassic/index.htm

Departamento de Tecnologa Electrnica

15

Diseo de circuitos digitales con VHDL - v1.01 - 20/07/10

FPGA

Conector JTAG

Conector de expansin

Memoria Flash

VGA

Alimentacin Jumpers de configuracin PS/2 Puerto accesorio Pulsadores LEDs Interruptores Display 7 segmentos

Figura 2.1: Placa Pegasus de Digilent

Amedidaquevayamosavanzandoconlaprcticairemosaprendiendolafuncionalidad delaplaca.Anas,sitienescuriosidad,enlapginawebdeDigilentpuedesconsultarel manualdelaplacaeningls[19]. 2.1.2. La tarjeta Basys La tarjeta Basys contiene una FPGA de Xilinx de modelo Spartan3E XC3S100E XC3S250E con encapsulado TQ144. Estas FPGA tienen respectivamente 100000 250000 puertaslgicasequivalentesy108pinesdisponiblesparaelusuario. La placa Basys tiene muchos perifricos similares a la Pegasus, por ejemplo: 8 LED, 4 displaysde7segmentos,4pulsadores,8interruptores,unpuertoPS/2yunpuertoVGA. Los puertos de expansin son diferentes a la Pegasus, la tarjeta Basys tiene 4 puertos de expansindetipoPMOD,conlosquepodemosconectarunagranvariedaddeperifricos disponibles4 o incluso podemos hacrnoslos nosotros mismos. La Pegasus slo tiene un puertoPMOD.Enlafigura2.2semuestralarevisinEdelaplacaBasys,enellasesealan variosdesuscomponentes.

4

LosconectoresPMODsonmuyvariados:pantallasdecristallquido,circuitoscontroldemotores,antenas, joysticks,amplificadoresdeaudio,micrfonos,etc.Sepuedenveren http://www.digilentinc.com/Products/Catalog.cfm?NavPath=2,401&Cat=9

16

Universidad Rey Juan Carlos

2. Encender un LED

FPGA

Conectores PMOD

Jumpers de configuracin Jumpers para la frecuencia del reloj

PS/2 USB

VGA

Interruptor para encender la tarjeta Interruptores LEDs Pulsadores

Displays 7 segmentos

Figura 2.2: Placa Basys de Digilent

2.2. Cmo encender un LEDDel ao pasado ya sabemos encender un LED. Ya hemos visto que las placas Pegasus y Basys tienen 8 LED disponibles para utilizar, cada uno de estos LED van conectados a distintospinesdelaFPGA.LaconexindelosLEDsemuestraenlafigura2.3.Enellase indicanqupinesdelaFPGAestnconectadosalosLED.PorejemploelLEDnmero0 de la Pegasus est conectado al pin 46. Para facilitar esta identificacin, la placa Pegasus lleva impresos la identificacin del LED y el pin asociado de la FPGA (en la Basys no5). As, podemos ver cmo al lado del LED 0 (LD0) de la Pegasus est el nmero 46 entre parntesis. Podemos apreciar que esto se cumple para casi todos los componentes: pulsadores,interruptores,....EstonoocurreenlaBasysyparaellatenemosqueconsultar sumanualdereferencia.PEGASUS'1' Encendido '0' Apagado 390 Spartan-II PIN 46 45 44 43 42 41 37 36 LED LD0 LD1 LD2 LD3 LD4 LD5 LD6 LD7 '0' Apagado 390

BASYS'1' Encendido Spartan-3E PIN 15 14 08 07 05 04 03 02 LED LD0 LD1 LD2 LD3 LD4 LD5 LD6 LD7

Figura 2.3: Conexin de los LED de la placa Pegasus (izquierda) y la Basys (derecha)

Viendoelesquemaelctricodelafigura2.3podemosdeducirquesiponemosun1lgico enelpin46delaFPGAdelaPegasusencenderemoselLED,yaque conun1 lgicola FPGApondrunatensinde3,3voltiosenesepin(queeselniveldetensindeesepin de la FPGA). Por el contrario, si ponemos un 0 lgico en el pin 45, mantendremos apagadoelLED1(LD1),puestoquenocircularcorrienteporl.5

TencuidadoporquelaBasysvieneconundibujoconlacorrespondenciaconlospines,yalgunosdeellos estnmal.Esmsseguroconsultarlosenelmanualdereferencia.

Departamento de Tecnologa Electrnica

17

Diseo de circuitos digitales con VHDL - v1.01 - 20/07/10

Aspues,steserelobjetivodelprimerejercicio,ponerun1enelpin46yun0enel pin45(paralaBasyslospondremosenlospines15y14respectivamente).Sidespusde programar la FPGA el LED 0 se enciende y el LED 1 se apaga habremos cumplido el objetivo. Con el resto de pines que van a los otros LED no haremos nada, en teora, hacindolo as no deberan lucir, ya que por defecto la FPGA pone resistencias de pull downenlospinesnoconfigurados,yunaresistenciadepulldownponelasalidaatierra.

2.3. Diseo del circuitoEldiseodelcircuitoloharemosconlaherramientaISEFoundationoconISEWebPackde Xilinx, esta ltima es la versin gratuita que se puede descargar en la pgina web de Xilinx.Estaprcticaestreferidaalaversin9.2,debidoaqueexistennuevasversiones, puedesdescargarestaversinen:http://www.xilinx.com/ise/logic_design_prod/classics.htm ParaarrancarelprogramapincharemoseneliconodeXilinxobien,desde:InicioTodos los programasXilinx ISE 9.2iProject Navigator

Nos puede aparecer una ventana con el Tip of the day que son indicaciones que hace la herramientas cada vez que la arrancamos. Si las leemos habitualmente podemos ir aprendiendopocoapoco.PinchamosenOk,conloquesecierradichaventana. Normalmente la herramienta abre el ltimo proyecto que se ha realizado. As que lo cerramospinchandoen:FileClose Project. Para empezar a crear nuestro nuevo proyecto, pinchamos en FileNew Project... y nos saldr la ventana New Project Wizard Create New Project como la mostrada en la figura 2.4.Enellapondremoselnombredelproyecto,quelollamaremos led0,indicamoslaruta donde guardaremos el proyecto, que ser C:/practicas/ed2/tunombre. Respecto al nombreyalaruta,esconveniente: NotrabajardesdeundispositivodememoriaUSB6. Noincluirespaciosenlaruta,portanto,estoincluyenotrabajarenel "Escritorio"ni en"Mis documentos" Noincluirenlarutaoenelnombreacentosniees,nicaracteresextraos,ninombres muylargos,lomsconvenienteeslimitarseacaracteresalfanumricos,yusarelguin bajoenvezdelespacio. Paraelltimorecuadrodelaventana,dondeponeTopLevelSourceTypeseleccionaremosHDL,yaquenuestrodiseoloharemosmediantelenguajesdedescripcindehardware7.

6

Sieststrabajandoenellaboratorio,alterminarlasesinnoolvidescopiarlosficherosconextensin.vhdy .ucfentumemoriaUSBoentucorreoelectrnico(ocupanmuypoco).Delocontrario,elprximoda puedeserquelosficheroshayandesaparecido. HDL:delingls:HardwareDescriptionLanguage

7

18

Universidad Rey Juan Carlos

2. Encender un LED

Figura 2.4: Ventana para la creacin de nuevo proyecto

Unavezquehemosrellenadolostresrecuadrospinchamosen Next.Ahoranosaparecela ventana de seleccin del dispositivo (figura 2.7). En Product Category ponemos All. En la familiaponemos:Spartan2sitenemoslaPegasus

Spartan3EsiusamoslaBasys Los siguientes datos los podemos obtener a partir de la observacin del texto del encapsuladodelaFPGA,quesemuestranenlafigura2.5paralaPegasusylafigura2.6 para la Basys. Hay que observar los valores que tiene la FPGA de nuestra placa, ya que por ejemplo, en la Pegasys en algunas el tipo es XC2S200 y en otras es XC2S50. Lo mismo sucedeconlavelocidad,enalgunases5yotras6.

tipo de dispositivo encapsulado velocidad rango de operacin C: comercial

XC2S200 PQ208

cdigo de fecha cdigo de lote

tipo de dispositivo encapsulado velocidad rango de operacin C: comercial

XC3S100E TQG144

cdigo cdigo

5C

4C

Figura 2.5: Interpretacin del texto del encapsulado de la FPGA de la Pegasus

Figura 2.6: Interpretacin del texto del encapsulado de la FPGA de la Basys

Paralaseleccindelaherramientadesntesisnotenemosalternativa,yparaelsimulador en esta prctica no es importante y lo dejamos en ISE Simulator (VHDL/Verilog). En el lenguajededescripcindehardwarepreferido(PreferredLanguage)sedejaelVHDL,quees elqueusaremos.AlterminarpinchamosenNext.

Departamento de Tecnologa Electrnica

19

Diseo de circuitos digitales con VHDL - v1.01 - 20/07/10

Pegasus Family Device Package Speed Spartan2

Basys Spartan3E

Mirar en la FPGA PQ208 TQ144

Mirar en la FPGA