005_Circuitos Secuenciales

-

Upload

pepe-campos -

Category

Documents

-

view

252 -

download

0

Transcript of 005_Circuitos Secuenciales

-

8/18/2019 005_Circuitos Secuenciales

1/35

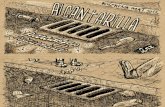

CIRCUITOS SECUENCIALESIntroducción a los Circuitos Lógicos

Programables

Pedro Ignacio Martos

1

-

8/18/2019 005_Circuitos Secuenciales

2/35

CONTENIDO Circuitos secuenciales

Maquinas de estado (Finite State Machines –

FSM)

Maquinas de estado con camino de datos (Finite

State Machines with Datapath – FSMD)

El Microcontrolador como circuito FSMD

2

-

8/18/2019 005_Circuitos Secuenciales

3/35

CIRCUITOS SECUENCIALES

Un circuito combinacional es un circuito

en el que la salida depende solo de las

entradas.

Un circuito secuencial es un circuito con

algun tipo de memoria, la cual establece

su “estado interno”.

La salida de un circuito secuencial

depende de su entrada y del estado

interno del mismo.

3

-

8/18/2019 005_Circuitos Secuenciales

4/35

CIRCUITOS SECUENCIALES Los circuitos secuenciales pueden ser sincrónicos

o asincrónicos

Sincrónicos: todos los elementos de memoria son

controlados por una señal externa denominada

“Reloj” (clock – CK) y almacenan sus datos en el

flanco ascendente o descendente del mismo.

Asincrónicos: la señal de control de los elementos de

memoria no es común a todos y/o es generada

internamente por el circuito secuencial.

La gran mayoria de los circuitos secuenciales son

sincrónicos, ya que permiten desacoplar/aislar el

almacenamiento respecto del resto del circuito.4

-

8/18/2019 005_Circuitos Secuenciales

5/35

CIRCUITOS SECUENCIALES El elemento de memoria mas básico de un

circuito secuencial es el Flip-Flop D (FF-D)

El valor de la entrada se muestrea en el flanco ascendente

del reloj (CK) y se almacena en el FF

Pueden tener una señal asincronica RESET (R) y una señal

sincrónica ENABLE (en)5

-

8/18/2019 005_Circuitos Secuenciales

6/35

CIRCUITOS SECUENCIALES Diagrama en bloques de un circuito secuencial

sincrónico:

6

-

8/18/2019 005_Circuitos Secuenciales

7/35

CIRCUITOS SECUENCIALES State Register: Grupo de FF controlados por una

señal CK, la salida de estos FF representa el

estado interno.

Next State Logic: Circuito combinacional que

determinar el nuevo valor del State Register.

Output Logic: Circuito combinacional que toma la

entrada externa y el estado interno para

determinar el valor de salida.

7

-

8/18/2019 005_Circuitos Secuenciales

8/35

M AQUINAS DE ESTADO Las “Maquinas de Estado Finito” (FSM) se utilizan

para modelizar sistemas que tienen una cantidad

finita de estados internos.

La aplicación principal de las FSM es laim lementación de controladores de sistemas

digitales complejos y se implementan mediante

circuitos secuenciales sincrónicos

Si la salida de la FSM solo depende de su estado

interno, se denomina “Maquina de Moore”; si lasalida depende del estado interno y de la entrada,

se denomina “Maquina de Mearly”. Ambos tipos de

salida pueden estar presentes en la FSM, por lo que

en general se denominan “Salida Mearly” y “Salida

Moore”

8

-

8/18/2019 005_Circuitos Secuenciales

9/35

M AQUINAS DE ESTADO Representación: Las FSM se representan

mediante diagramas de estado, que contienen:

Nodos: Representan un estado interno y en el

diagrama se visualizan mediante circulos

Arcos: Cada arco re resenta una función ló ica de las

entradas y el estado interno del cual sale el arco.

Cuando la función se evalua como verdadera, se pasa

al nodo al que llega el arco

La salida Moore va en los nodos, ya que solodepende del estado interno

La Salida Mearly va en los arcos, ya que depende

del estado interno y de la entrada9

-

8/18/2019 005_Circuitos Secuenciales

10/35

M AQUINAS DE ESTADO Representación gráfica:

10

-

8/18/2019 005_Circuitos Secuenciales

11/35

M AQUINAS DE ESTADO Representación gráfica:

11

-

8/18/2019 005_Circuitos Secuenciales

12/35

M AQUINAS DE ESTADO Ejemplo: FSM para controlar dos semaforos.

El sistema tiene 3 modos de funcionamiento:

Normal, Test, e Intermitente

En Normal hay 8 estados, que representan las luces

para pasar de un estado al siguiente

En Test estan los mismos 8 estados y tiempos entre

transiciones que en normal, pero el tiempo para

cambiar entre estados es siempre de 1 segundo, de

manera de poder probar el sistema.

En Intermitente las luces amarillas parpadean cada

2 segundos mientras la señal de intermitente este

activada

Se asume que hay un clock de 50Hz disponible

12

-

8/18/2019 005_Circuitos Secuenciales

13/35

M AQUINAS DE ESTADO Diagrama de Estados

13

-

8/18/2019 005_Circuitos Secuenciales

14/35

M AQUINAS DE ESTADO Implementacion en VHDL

14

-

8/18/2019 005_Circuitos Secuenciales

15/35

M AQUINAS DE ESTADO Implementacion en VHDL

15

-

8/18/2019 005_Circuitos Secuenciales

16/35

M AQUINAS DE ESTADO Implementacion en VHDL

16

-

8/18/2019 005_Circuitos Secuenciales

17/35

M AQUINAS DE ESTADO FINITO CON

CAMINO DE DATOS (FSMD) Una FSMD combina una FSM con un circuito

secuencial.

La FSM, que es el “camino de control” (control

path) toma las entradas (comandos) y el estadointerno enera señales de control ue es ecifican

las operaciones en el circuito secuencial ,

denominado “camino de datos” (datapath)

Una FSMD se utiliza para implementar sistemas

descriptos mediante “transferencia de registros”(Register Transfer Metodology - RTM)

En RTM se definen operaciones como manipulacion

y transferencia de datos entre registros 17

-

8/18/2019 005_Circuitos Secuenciales

18/35

OPERACIONES EN RTM Una operación en RTM especifica una

manipulación de datos y transferencia hacia un

registro mediante una función:

Rdest: registro de destino

Rsrc1…rsrcn: registros con datos a manipular

F(.): operación a realizar sobre los registrosfuente.

18

-

8/18/2019 005_Circuitos Secuenciales

19/35

OPERACIONES EN RTM – EJEMPLOS

19

-

8/18/2019 005_Circuitos Secuenciales

20/35

OPERACIONES EN RTM Una operación se implementa mediante un

circuito combinacional para la funcion f(.) y

conectando dicho circuito a los registros fuente y

destino

–

20

La funcion f(.) involucra un restador y un

incrementador .

La operación esta sincronizada por un reloj (CK)

El resultado se almacena en el registro destino en

el siguiente flanco de ck.

-

8/18/2019 005_Circuitos Secuenciales

21/35

OPERACIONES EN

RTM Diagrama en bloques:

21

-

8/18/2019 005_Circuitos Secuenciales

22/35

OPERACIONES EN

RTM Un circuito basado en RTM especifica qué

operaciones se realizan entre registros a cada

ciclo de reloj

Esto es similar a la transición entre estados de

22

,

representar la secuencia de operaciones RTM

-

8/18/2019 005_Circuitos Secuenciales

23/35

OPERACIONES EN

RTM Otro Ejemplo:

23

-

8/18/2019 005_Circuitos Secuenciales

24/35

-

8/18/2019 005_Circuitos Secuenciales

25/35

RTM Y

FSMD El camino de control es una FSM, por lo que

contiene:

Registro de estado (almacena el estado interno)

Lógica de siguiente estado (next-state logic)

25

La entrada son las señales de comando externas y el

estado del camino de datos

La salida son las señales de control del camino de

datos Aunque la FSMD tiene dos circuitos secuenciales,

ambos estan controlados por el mismo reloj, por

lo que es un circuito sincrónico.

-

8/18/2019 005_Circuitos Secuenciales

26/35

FSMD Diagrama en bloques:

26

-

8/18/2019 005_Circuitos Secuenciales

27/35

FSMD Y

MICROPROCESADOR

En una FSMD todos los componentes (registros,

ruteo, unidades funcionales, entrada, etc) están

diseñados para una aplicación especifica.

,

utilizar software para implementar una FSMD

capaz de realizar distintas aplicaciones.

La transformación a una FSMD “universal” se

realiza de la siguiente manera:

27

-

8/18/2019 005_Circuitos Secuenciales

28/35

FSMD Y MICROPROCESADOR

Se reemplaza el camino de datos específico por

una configuración fija.

Los registros de datos y la red de ruteo se

reemplazan por un conjunto fijo de registros que

salida.

Las unidades funcionales se reemplazan por una

ALU (Arithmetic & Logic Unit) que solamente

puede realizar un conjunto predefinido defunciones

28

-

8/18/2019 005_Circuitos Secuenciales

29/35

FSMD Y MICROPROCESADOR

De esta manera el camino de datos ahora realizar

operaciones del tipo

, r y r son os reg s ros uen e y es no

Op es una de las operaciones de la ALU

Se reemplaza la FSM con una maquina de estados

“programable”:

El estado interno pasa a ser el “program

counter”, su contenido representa el estado

interno de camino de control29

-

8/18/2019 005_Circuitos Secuenciales

30/35

FSMD Y MICROPROCESADOR

En una FSM cada estado genera salidas para

controlar las operaciones del camino de datos , estas

salidas pasan a ser “instrucciones” y se almacenan en

una “memoria de programa”.

Cada direccion de memoria de la memoria deprograma representa un estado (valor) del program

counter .

Durante la ejecución, la instrucción apuntada por el

program counter es recuperada de la memoria de

programa y decodificada para generar las señales decontrol del camino de datos

Asi, la “output logic” de la FSM es reemplazada por

la memoria de programa y la logica de decodificación 30

-

8/18/2019 005_Circuitos Secuenciales

31/35

FSMD Y MICROPROCESADOR

En la FSM programable el siguiente estado es el valor

del estado actual + 1 (el program counter se

incrementa en 1), lo que muestra la naturaliza

secuencial de este sistema.

Esta secuencialidad solo se altera medianteinstrucciones especiales, denominadas “saltos”, en los

cuales el program counter se carga con un nuevo valor

De esta manera, la “next-state logic” de la FSMD es

reemplazada por el incrementador unitario y la logica

de multiplexado para cargar un nuevo valor.

31

-

8/18/2019 005_Circuitos Secuenciales

32/35

FSMD Y MICROPROCESADOR

Diagrama en bloques de la transformación (ANTES):

32

-

8/18/2019 005_Circuitos Secuenciales

33/35

FSMD Y MICROPROCESADOR

Diagrama en bloques de la transformación (DESPUES):

33

-

8/18/2019 005_Circuitos Secuenciales

34/35

FSMD Y MICROPROCESADOR

Diagrama en bloques del microprocesador AVR:

34

-

8/18/2019 005_Circuitos Secuenciales

35/35

FSMD Y MICROPROCESADOR Diagrama en bloques del microcontrolador AVR:

35