tarea2_v5

-

Upload

nicolas-novalic -

Category

Documents

-

view

214 -

download

2

description

Transcript of tarea2_v5

-

Introduccin a los Microprocesadores Facultad de Ingeniera UDELAR 2015

Tarea 2 | Entorno de desarrollo de hardware

Objetivos Familiarizarse con el uso de la herramienta Quartus para agregar puertos de entrada

y salida a un sistema dado.

Descripcin GeneralEl objetivo de la tarea consiste en agregar dos puertos al sistema inicial suministrado con el Tutorial de hardware.

Antes de comenzar el estudiante deber tener instalado el Quartus y haber seguido todos los pasos de la gua del laboratorio Tutorial de hardware.

Luego deber repetir el procedimiento partiendo nuevamente del sistema inicial suministradocon el tutorial. En esta oportunidad se deben agregar los siguientes dos puertos:

Un puerto de salida que maneje las salidas LEDG[7..0] de la placa, mapeado en la direccin dirout del espacio de salida.

Un puerto de entrada mapeado en la direccin dirin del espacio de entrada, conectado a las salidas del registro del puerto de salida pedido arriba. Observar que al leer este puerto de entrada con con la instruccin IN A, (dirin) debe obtenerse el ltimo valor escrito en el puerto de salida y NO el valor de los switches que no se utilizan en este caso.

Ambos puertos deben estar decodificados sin fantasmas.

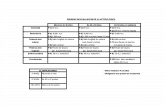

Las direcciones dirout y dirin de los puertos se determinan a partir de la cdula de identidad de cada estudiante como sigue:

Si los dgitos de la cdula de identidad son d6 . d5d4d3 . d2d1d0 (NO se considera el dgito verificador), entonces, dirout es el nmero obtenido haciendo el OR entre la constante 0x80y el nmero 0xd3d2 (la notacin 0x indica nmeros hexadecimales (base 16)) y dirin haciendo el OR entre 0x80 y el nmero 0xd1d0.

Por ejemplo: para la cdula de identidad 1.234.567 los valores de las constantes son:

dirout = 0xd3d2 OR 0x80 => dirout = 0x45 OR 0x80 => dirout = 0xC5 (1100 0101B)

dirin = 0xd1d0 OR 0x80 => dirin = 0x67 OR 0x80 => dirin = 0xE7 (1110 0111B)

Observar que por la forma en que se obtienen, los valores de dirout y dirin son mayores o iguales a 0x80 y por lo tanto no hay posibilidad de conflicto con los otros puertos presentes en el sistema suministrado con el tutorial (DFF y Bridged_jtag_uart).

Para verificar si el circuito funciona correctamente se sugiere escribir un programa de prueba que escriba un valor de prueba (p. ej. 0x55 = 01010101B o 0xAA = 10101010B) en elpuerto dirout y luego lea desde el puerto dirin para verificar que se lee el mismo valor de prueba.

Tarea 1 ver. 2015-04-23 Pag. 1/2

-

Introduccin a los Microprocesadores Facultad de Ingeniera UDELAR 2015

Para la correccin se cargar en el FPGA el archivo demo-hw.sof entregado por el estudiante y se verificar con programas de prueba que los puertos estn mapeados en las direcciones correspondientes al nmero de cdula del estudiante (y solamente en esas direcciones).

Entrega

La entrega consistir de un archivo comprimido (zip) con los siguientes archivos del diseo realizado por el estudiante

sistema.bdf

demo-hw.sof

demo-hw.qsf

El archivo comprimido debe tener como nombre el nmero de C.I. (sin puntos ni guiones y SIN el dgito verificador) y debe llevar la extensin .zip. Por ejemplo si el nro. de cdula es 1.234.567-8 el archivo debe llamarse 1234567.zipEl archivo debe subirse a travs de la tarea que ser creada en la pgina del curso en la plataforma EVA de facultad. La entrega vence el da viernes 15 de mayo a las 23:55hs.

Tarea 1 ver. 2015-04-23 Pag. 2/2

Tarea 2 | Entorno de desarrollo de hardwareObjetivosDescripcin GeneralEntrega