Diseño de S.E. usando placa Lanín

description

Transcript of Diseño de S.E. usando placa Lanín

Presentacin de PowerPoint

Diseo de S.E. usando placa LannEmTech S.A.1Que es un sistemas embebido?Un sistema embebido se puede definir como un sistema electrnico diseado especficamente para realizar determinadas funciones.El hardware y el software estn diseados y optimizados para resolver un problema en concreto.Su caracterstica es que emplea uno o varios procesadores digitales, pudiendo ser un microprocesador, microcontrolador o DSP.Generalmente en un sistema embebido el hardware y el software estn diseados y optimizados para resolver un problema en concreto. Por parte del hardware se busca minimizar su tamao, reducir su consumo de energa (puede ser alimentado por bateras) y emplea componentes especficos para resolver el problema.Respecto al software se debe tener en cuenta que se dispone de recursos limitados (memoria, capacidad de clculo, etc.) por lo que se debe realizar un estudio previo en la fase de diseo para determinar que dispositivo y que metodologa de programacin es el adecuado (Usar o no un sistema operativo)

2Donde encontramos un sistema embebido?AplicacionesElectrodomsticosJuguetesInstrumentacinAutomatizacinVehculosSector AeroespacialComunicacionesRobticaCul es la arquitectura de un sistema embebido?CPUComunicacionesEntrada/SalidaInterfaz con el usuarioAlimentacinEl microcontrolador, microprocesador, dsp es el dispositivo que le da inteligencia al sistema, y que permite ser programado para realizar las funciones especficas. En el mercado actualmente hay muchas opciones, de 8-bits, 16-bits, 32-bits, distintas capacidades de clculo, distintas arquitecturas, de consumo reducido de energa, etcComunicaciones. Esto permite comunicar el sistema embebido con otros sistemas embebidos, sensores, usuario, etc Entre las ms conocidas tenemos, comunicacin serial, USB, Ethernet, bluetooth, GPRS, etc.Entrada y salida. Mdulos que se encargan de enviar o hacer llegar seales al CPU realizando el procesamiento adecuado para la lectura de sensores, activacin de actuadores, etc. Pueden ser digitales o analgicos. Interfaz con el usuario. Algunos sistemas necesitan interaccin con el usuario y entre estos dispositivos tenemos: Leds, botones, LCD alfanumrico, pantalla grfica, pantalla tctil, etc. Alimentacin. Es el modulo que se encarga de generar los distintos niveles de tensin para alimentar cada uno de los dispositivos dentro del sistema embebido, compuesto por reguladores de tensin, filtros de interferencias, circuitos supervisores de tensin, protectores de sobretensin, etc. 4Placa Lann

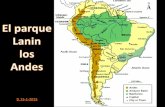

Durante el transcurso del curso vamos a utilizar la placa Lanin, placa desarrollada por Emtech que permita realizar aplicaciones personalizadas disponiendo de los recursos necesarios para un rpido desarrollo y permitiendo adems agregar otros mediante la creacin de placas hijas6

ARM7Que es ARM? ARM es un empresa que se dedica al diseo de cores y algunos otros aditamentos (perifricos, controladores de memoria, etc), pero no a la fabricacin de chip.

Como corazn se utiliza un microcontrolador ARM de la empresa ST. Que es ARM? ARM es un empresa que se dedica al diseo de cores y algunos otros aditamentos (perifricos, controladores de memoria, etc), pero no a la fabricacin de chip.Ellos se dedican a vender estos diseos los cuales se pueden adaptar a diferentes productos, y son las empresas que dependiendo de la estrategia que utilice seleccionara los perifricos para diferenciarse de otras que utilizan el mismo procesador.

8Empresas consumidoras de arquitecturas ARM

Familias de arquitecturas ARM

ARM a partir de su arquitectura v7 introduce el concepto de perfiles denotndolo por una letra en su nomenclatura:A: Procesador de alta performance orientados a sistemas complejos.R: Procesadores orientados a sistemas de tiempo real o de seguridad critica.M: Procesadores orientados a microcontroladores, de arquitectura ms sencillas

10Cortex-M

Los que nos interesa en este curso son los Cortex M y actualmente est compuesta por:Cortex M0, M0+, M1, M3, M4.M1 solo se puede usar como softcore dentro de una FPGA.

11Cortex-M

Las modificaciones y diferencias de esta arquitectura estn fundamentalmente enfocadas a obtener una operacin determinstica, mnima latencia de interrupciones, contar con una pipeline mnima y prescindir del uso de caches.El set de instrucciones est diseado para soportar de forma simple y eficiente la gran mayora de las operaciones realizadas en lenguaje C, incluyendo bitfields. Un micro con un set de instrucciones diseado para que el compilador pueda generar cdigo eficiente en la mayora de las operaciones tpicas que se desarrollan en CPresenta un mapa unificado de memoria, lo que le permite ocultar su estructura Harvard a los oj os del programador (y fundamentalmente del compilador). La definicin del mapa de memoria por parte del proveedor del core (ARM), permite que todos los fabricantes que lo utilizan ubiquen tanto memoria como perifricos en las mismas direcciones (en general). Esto, sumado a la existencia de perifricos comunes como el NVIC (Nested Vectored Interrupt Controller) y el timer Sy sTick , y el software de abstraccin CMSIS (Cortex Microcontroller Software Interface Standard), logran que el usuario final pueda portar su aplicacin de un fabricante a otro sin may ores inconvenientes. Esto es tal vez la mayor fortalez a de ARM en microcontroladores, el usuario no queda atado a un fabricante ni a una herramienta de desarrollo.

12Cortex-M

Modelo de manejo de prioridadesCada excepcin tiene un nivel de prioridad, y slo aqullas de mayor prioridad pueden interrumpir a otra que est siendo atendida. Los nmeros ms bajos tienen precedencia, es decir, una prioridad ms alta. Las excepciones Reset, NMI y HardFault, segn vimos, tienen las prioridades ms altas, fijas e inamovibles, -3, -2 y -1 respectivamente. El resto de las excepciones permite que su prioridad se pueda configurar por software mediante registros en el SCB o el NVIC, comenzando con el valor 0 (la prioridad ms alta). ARMv7-M se orienta a microcontroladores, y un buen manejo de interrupciones anidadas con baja latencia es una pieza fundamental en una buena arquitectura. Con esta finalidad, se incorporan una serie de caractersticas nicas, a saber:Tail chaining (encadenado a la cola): Permite pasar de atender una excepcin a otra sin recuperar y volver a salvar los registros que ya han sido salvados (R0 a R3, R12, LR y PC).Late arrival (arribo tardo): Permite atender primero a una excepcin de mayor prioridad que se produce durante el proceso de guardar los registros en el stack en atencin a una excepcin anterior, de menor prioridad.POP pre-emption (suspensin de la recuperacin de registros del stack ): Si una excepcin ocurre en medio del proceso de recuperacin de registros del stack , como consecuencia del retorno del procesamiento de una excepcin anterior, es posible interrumpir dicho proceso y atender la nueva excepcin inmediatamente

13

La placa Lann est desarrollada utilizando un ARM Cortex M4 STM32F417ZGT6 de la empresa ST. El procesador M4 es una de las implementaciones de la arquitectura ARMv7-M. Cortex-M4 es el resultado de la evolucin de la arquitectura Cortex-M3 de ARM de 32-bits, sus microcontroladores se caracterizan principalmente por proporcionar capacidades para el procesamiento de seal digital (DSP), funcionalidad matemtica y una unidad opcional de punto flotante (FPU). Esta es una caracterstica que agrega M4 pero que no todos los fabricantes la incorporan.FPU: Este bloque opcional agrega un conjunto extra de treinta y dos registros para nmeros en coma flotante de simple precisin (32-bits). Entre las cuales encontramos suma y multiplicacin en un ciclo de clock , divisin en catorce ciclos, y multiplicacin y acumulacin en tres ciclos de clock .Adicionalmente, la arquitectura Cortex-M4 cuenta con mejoras respecto a eficiencia energtica, lo que representa un aspecto de vital importancia en el desarrollo de tecnologas modernas, siempre apuntando al cuidado del medio ambiente.

14

15

4 LEDs y 2 Pulsadores

Ideales para corroborar el correcto funcionamiento de las diferentes aplicaciones, para ingresar estmulos externos a la aplicacin o como interfaz de usuarioConexin en los puertos del microcontrolador

Conexin USB host

Para conectar diferentes perifricos a la placa, tales como teclado, mouse, pendrive, etc.Conexin USB host con el microcontrolador

Se ha utilizado un controlador de corriente mxima, lo que permite habilitar/des-habilitar la alimentacin y detectar si ocurre una sobre-corriente (>500mA) al operar con el dispositivo.

19

Conexin RS 485Posee dos canales RS485 half-duplex RS485 es un bus de transmisin multipunto diferencial, ideal para transmitir a altas velocidades sobre largas distancias (35 Mbit/s hasta 10 metros y 100 kbit/s en 1200 metros) y a travs de canales ruidosos.

20Conexin RS 485 con el microcontrolador

Zcalo para memoria SDAlta capacidad de almacenamiento tanto para guardar datos de adquisiciones como para almacenamiento de paginas web, archivos de audio, etc.Las lneas utilizadas en este zcalo tambin se disponen en un conector, ya sea para debugger o para realizar una placa adicional que utilice estas lneas.

22Conexin SD

Conexin USB devicePara conexin de datos y alimentacin desde una PC. Adicionalmente permite utilizar el bootloader del microcontrolador.Conector mini-USB tipo B para implementar el sistema embebido como dispositivo USB. De esta manera podemos implementar alguna clase USB (CDC, HID, MSD) para comunicacin con una PC, permitiendo realizar aplicaciones para control y/o configuracin del mismo o para transferencia de datos.Adicionalmente el microcontrolador puede ser iniciado en modo bootloader y utilizar este medio de comunicacin para actualizar el firmware.La placa dispone de los jumper BOOT0 y BOOT1 para seleccionar desde donde bootear al resetear el microcontrolador. Las opciones son desde Flash (modo default), desde system Memory (que tiene el bootloader) o desde una memoria externa SRAM.

24Conexin USB device

EthernetEthernet 10/100Mbps para implementacin de stack TPC/IPDispone de un conector Ethernet 10/100 Mbps con trasformadores incluidos para la implementacin del stack tcp/ip. Esto permite embeber pginas web ya sea para visualizar el estado del sistema o para configurar sus funcionalidades. O implementar protocolos TCP/UDP para la transferencia de datos o para implementar otros protocolos sobre ellos tales como Modbus, DNP3, etc.

26Conexin Ethernet

HeadersPines de uso general, compatibles con placas DTR desarrolladas por Emtech S.A. Implementa algunas lneas del perifrico FSMC para control de memoria Nand-Flash, Muxed-Nor-Ram o LCD

Se implementan dos conectores con un estndar establecido por Emtech para mantener en el desarrollo de placas de este estilo y poder generar placas hijas a ser utilizadas en cualquiera de ellos. Se disponen de 64 pines de entrada y salida que pueden usarse para propsitos generales y de las alimentaciones disponibles en la placa 3.3V y 5V.En la seleccin de pines a implementar en estos conectores se tuvo en cuenta los mnimos necesarios utilizados por el perifrico denominado FSMC (flexible static memory controller) para poder controlar una memoria Nand-Flash o Muxed-Nor-Ram. En el caso de una memoria multiplexada se puede direccionar hasta 2^26=64 MBytes.

28Conexin Headers

DTRs

DTRs

AlimentacinExterna o USB, seleccin mediante jumperSe dispone de dos conectores de alimentacin para una fuente externa de 5V, pero adicionalmente se puede seleccionar como fuente de alimentacin los 5V obtenidos de los conectores USB.

32

Serial/USB y JTAG/USBMediante un chip de FTDI se implementa la conversin de UART1 a USB para uso general y de JTAG a USB para programador/depurador on-board. Se agreg un chip de la empresa FTDI (FTH2232H). Este dispositivo USB tiene dos puertos con la capacidad de ser configurados en una gran variedad de interfaces serie o paralelo estndar de la industria. En este caso se utiliza un canal para comunicacin serial (USART1 del microcontrolador) y otro para JTAG lo que permite tener un programador/debugger on-board utilizando el server JTAG OpenOCD (cdigo abierto)

33

JTAGAdicionalmente se dispone del conector para utilizar un programador/depurador externo. Adicionalmente tambin se dispone de un conector JTAG con pin-out estndar para poder utilizar cualquier otro programador externo34Entorno de desarrolloQue es un entorno de desarrollo?Es aquel que permite integrar distintas herramientas de desarrollo dentro de un solo programa.Editor, compilador, depurador.Lann-CM4 SDK. (Eclipse)Entornos de desarrollo:KeilLa firma Keil es una empresa famosa por sus compiladores para MCS-51 (8051), desde hace unos aos una empresa del grupo ARM. Como tal, el compilador es algo as como el oficial, al menos para este entorno de microcontroladores. El entorno de desarrollo utilizado es uVision, el nombre del producto es ARM-MDK (Microcontroller Development Kit), del que puede obtenerse en pgina web una versin sin costo con lmite de 32KB de cdigo generado.IAR SystemsLa empresa sueca IAR Systems desarrolla el producto Embedded Work bench for ARM (EWARM), cuya versin sin costo con lmite de 32KB de cdigo generado. CooCoxDicho nombre hace referencia a Cooperate on Cortex, un grupo de desarrolladores que provee un entorno de distribucin gratuita, CoIDE, basado en Eclipse y la distribucin lite de Sourcery CodeBench de Mentor Graphics. Este grupo de desarrolladores provee adems cdigo para muchos perifricos, una capa de abstraccin (CoX), y hasta un RTOS (CoOS), todo de forma gratuita.

36Porque Eclipse?Cdigo abiertoInterfaz amigableExisten diferentes plugins que incrementan sus capacidades

37Configuracin de EclipseCdigo fuenteToolchainPlataformaCodeSourcery GNU YAGARTO GNU ARMConfiguracin de EclipseCodeSourcery GNU toolchain para ARM: Permite construir aplicaciones ARM embebidas. YAGARTO GNU ARM toolchain: Es una EABI (embedded-application binary interface). Esto especifica las convenciones estndares para formatos de archivos, tipos de datos, uso de registros, etc.Lanin-CM4 SDK

Diseo de aplicaciones en sistemas embebidosRecordandoAplicacionesElectrodomsticosJuguetesInstrumentacinAutomatizacinVehculosSector AeroespacialComunicacionesRobticaAplicacionesCualquier sistema puede clasificarse en :

Sistema sin requerimientos de respuestas en tiempo real.Sistemas con requerimientos flexibles de respuesta en tiempo real. Sistemas con requerimientos estrictos de respuesta en tiempo real.

N-RT: Es un sistema en los que no hay plazos involucrados. "Es un sistema en el que la reaccin programada a un estmulo sin duda ocurrir en algn momento en el futuro."Ej: Encontrar la solucin de una ecuacin matemtica.

Un sistema de tiempo real flexible es un sistema en el que el no cumplimiento de un plazo puede producir efectos no deseados, pero no catastrficos, una degradacin del rendimiento, por ejemplo. "Un sistema de tiempo real flexible es un sistema en el que la reaccin programada a un estmulo casi siempre se complet dentro de un tiempo finito conocido".

Un sistema de tiempo real estricto es un sistema en el que el no cumplimiento de un plazo puede tener efectos catastrficos. Es un sistema en el que est garantizada la reaccin a un estmulo programado para ser completado en un tiempo finito conocido".44Dos paradigmas de programacinBare MetalRTOSEl software tiene acceso directo sobre los recursos del hardware.Para llevar a cabo este mtodo en la placa Lann, se utiliza la librera CMSIS.

El software utiliza un sistema operativo RTOS.En nuestro ejemplo prctico en la placa Lann utilizaremos el ChibiOS.Tambin se pueden correr diferentes sistema operativos, por ejemplo: Nuttx, FreeRTOS. etc.

Nuestro sistema y bajo que restricciones de tiempo real se encuentras, se pasa a elegir bajo que paradigma de programacin se va a disear nuestra aplicacin. Bare Metal RTOS45El sistema embbebido ejecuta un solo programa con un objetivo nico. Ej:TErmmetros digitales,Controladores de juguetes,Controles de iluminacin automticos,Tarjeta de cumpleaos,El sistema operativo en si.Mtodo de programacin:

Qu nos ofrece el fabricante para interactuar con el uC?La CMSIS es una librera comn a todos los fabricantes de procesadores ARM Cortex-M y pretende establecer la abstraccin del hardware.

Core Peripheral Access LayerDevice Peripheral Access LayerAccess Functions for Peripherals (optional)

ARM provides as part of the CMSIS the following software layers that are available for various compiler implementations:

Core Peripheral Access Layer: contains name definitions, address definitions and helper functions to access core registers and peripherals. It defines also a device independent interface for RTOS Kernels that includes debug channel definitions. These software layers are expanded by Silicon partners with:

En principio necesitaremos algunas libreras que sirvan de interfaz para acceder a los componentes del microcontrolador.

Device Peripheral Access Layer: provides definitions for all device peripherals Access Functions for Peripherals (optional): provides additional helper functions for peripherals CMSIS defines for a Cortex-M Microcontroller System:

A common way to access peripheral registers and a common way to define exception vectors. The register names of the Core Peripherals and the names of the Core Exception Vectors. An device independent interface for RTOS Kernels including a debug channel. 47CMSISEstas libreras deben agregarse al proyecto creado en Eclipse, las cuales se encuentran comprimidas en un nico archivo titulado STM32F4 DSP and standard peripherals library.

Link de descarga:

http://www.st.com/stonline/stappl/resourceSelector/app?page=resourceSelector&doctype=FIRMWARE&SubClassID=1521

Bsicamente bajo este mtodo de programacin estamos por las nuestras, con la ayuda de las libreras de la CMSIS48

Algunos archivos de la librerasystem_stm32f4xx.c/.h Lugar donde se encuentra la configuracin del reloj para los dispositivos STM32F4xx. Exporta la funcin SystemInit() que configura el reloj, los factores multiplicadores y divisores del PLL, AHB / APBx prescalers y Flash. Esta funcin es invocada en la inicializacin justo despus del reset y antes de comenzar el programa principal. La llamada se realiza dentro del archivo startup_stm32f4xx.s. stm32f4xx.h Lugar donde se encuentran las definiciones de todos los registros de perifricos, bits de los registros, y mapeo de memoria para dispositivos STM32F4xx. Proporciona el cdigo de inicializacin del Cortex-M4 y los vectores de interrupcin para todos los manejadores de interrupcin del dispositivo STM32F4xx. startup_stm32f4xx.s Creacin de un proyecto en CPara comenzar cambiar el Workspace a Placa Lanin/BareMetal:

File -> Switch Workspace -> Others52Creacin del proyecto

EL NOMBRE SIN ESPACIOS53Importando libreras

Configuraciones

STM32F4XXUSE_STDPERIPH_DRIVER

*.ldProyecto terminado

Si se abre un ejemplo anteriormente compilado en otra PC, borrar la carpeta Debug.56Importar un proyecto

Configuracin del Debugger

arm-none-eabi-gdb

Antes de iniciar, compilar el ejemplo!58Pasos para debuggear una aplicacin

Ejemplos mtodo:

Configuracin generalLa inicializacin de cualquier perifrico en los cortex M4 consta de cuatro pasos bsicos:Programacin del reloj: En MCUs de muy bajo consumo, generalmente los perifricos tienen su seal de reloj inhabilitada.Programacin de configuraciones: Los pines del MCU son compartidos entre perifricos, salvo muy contadas excepciones.La conexin del perifrico a una fuente de reloj debe hacerse explcitamente mediante un registro de configuracin del procesador.

Este proceso se llama multiplexado y un registro de configuracin del procesador es el que determina hacia que perifrico debe apuntar el pin a usar61Configuracin generalConfiguracin del perifrico: Determinar las caractersticas particulares para el funcionamiento en una aplicacin especfica.Configuracin de la interrupcin: Si se tratan eventos del perifrico a travs de INTs, stas deben ser configuradas.En los cortex M4 esta configuracin se hace sobre el Nested Vector Interrupt Controller (NVIC). 62Configuracin de Pines de Entrada y Salida de propsito general GPIOEl uso de las GPIO son la forma ms fcil de interactuar con perifricos como botones, leds, interruptores, y otros componentes.De acuerdo al tipo de operacin que se desee realiza con las GPIO, se pueden configurar de acuerdo a los siguientes parmetros: Modo: Entrada, Salida, Anlogo, Funcin alternativa.Tipo del pin de salida: Push-pull, Open drain.Velocidad del pin de salida: Baja (2MHz), Media (10MHz), Alta (50MHz).Resistencias internas: Pull-up, Pull down.

La configuracion de velocidad es para ahorrar energa, ya que una configuracin de 2M consume menos energa que la de 50.63Configuracin de Pines de Entrada y Salida de propsito general GPIO

Cdigo para configuracin de las salidas digitalesEjercicio: Analizar y ejecutar el ejemplo del demo de prendido y apagado de leds.

Entradas digitalesModificar el ejemplo para cambiar el estado de un led cada vez que se pulse S2.Ayuda: Manual de la STM32F4 DSP and standard peripherals library (stm32f4xx_dsp_stdperiph_lib_um.chm)

if(GPIO_ReadInputDataBit(GPIOG, GPIO_Pin_15)==1){ GPIO_ToggleBits(GPIOG,GPIO_Pin_3);Delay(5000); }66Configuracin de la USART

Cdigo para configuracin de la USART

Entradas analgicas3 conversores AD19 canales multiplexados (16 externos)Hasta12 bits de resolucinMuchos modo de funcionamiento:Simple, continuo, disparo interno, externo, temporizado, ...Transferencia por programa, interrupcin, DMAModos entrelazados, simultneosCanales regulares e inyectados

Hay 16 canales multiplexados. Es posible organizar las conversiones en dos grupos: regular y de inyecta. Un grupo consiste en una secuencia de conversiones que se pueden hacer en cualquier canal y en cualquier orden. Por ejemplo, es posible llevar a cabo la conversin secuencia en el orden siguiente: ADC_IN3, ADC_IN8, ADC_IN2, ADC_IN2, ADC_IN0, ADC_IN2, ADC_IN2, ADC_IN15. Un grupo regular se compone de hasta 16 conversiones. Un grupo de inyecta se compone de un mximo de 4 conversiones. 70Configuracin ADC

Mtodo de programacin:

SISTEMA OPERATIVO RTOSSistema Operativo en Tiempo Real RTOSUn RTOS, es un Sistema Operativo especializado en operaciones de respuesta en tiempo real y debe cumplir con las siguientes caractersticas:

Respuesta de tiempo Previsible.Determinista.Es importante entender que el diseo del sistema en s, es lo que lo hace, estricto, flexible a las restricciones de tiempo real, el RTOS es slo una herramienta que se puede utilizar de forma correcta o incorrecta.

En su sistema, puede utilizar un RTOS simplemente porque puede ser cmodo de usar en comparacin con un sistema de metal desnudo. Un RTOS, especialmente diseado para aplicaciones integradas, tambin puede ofrecer otros servicios como, por ejemplo, un entorno de ejecucin estable, controladores de dispositivos, sistemas de archivos, redes y otros subsistemas tiles.

Determinista: Ningn factor externo podra modificar su comportamiento.Respuesta de tiempo previsible: Es posible calcular el tiempo en que se demorara en ejecutar alguna tarea.73Ejemplo de Sistema en tiempo RealEntorno ExternoSensoresActuadoresSoftware de Tiempo RealTareaTareaTareaSORelojEj: Sistema de control de un automvil.RTOSUn RTOS permite disear la aplicacin por bloques funcionales, donde cada bloque en teora sera un hilo (thread).Cada hilo se responsabilizara de una parte de la aplicacin, respondiendo a diferentes restricciones de tiempo, por lo cual debern tener diferentes prioridades.Un SO ofrece las ventajas de asegurar la correcta ejecucin de tareas de tiempo real con tiempos de ejecucin crticas, las cuales no se ven afectadas por la ejecucin de tareas con menos prioridad. RTOSUn sistema operativo, ofrece, la posibilidad de asignar prioridades a las tareas, as como los mecanismos para que se comuniquen entre ellas, y las herramientas que aseguren que las tareas que tienen tiempo crtico, sean ejecutadas dentro de las restricciones de tiempo real establecidas.

Caractersticas de un RTOSTiempo de Respuesta: Un RTOS eficaz slo aade una pequea sobrecarga en el tiempo de respuesta mnimo terico del sistema por ejemplo: El tiempo desde una peticin de interrupcin y el de interrupcin. El tiempo de un evento de hardware, por lo general una interrupcin y el reinicio de la tarea que debe manejarlo.El tiempo de cambio de contexto, necesario para cambiar de forma sincronizada desde el contexto de un hilo en el contexto de otro hilo.Bajo Jitter.Tamao: Un RTOS ms compacto es preferible siendo todos los dems parmetros iguales, por el costo de memoria.Confiabilidad: Algunos sistemas pueden ser ms fiables que otros, la asignacin dinmica es un buen ejemplo, tanto falta de fiabilidad y el tiempo de imprevisibilidad.Primitivas de Sincronizacin: Variedad de primitivas disponibles para utilizar.

Tiempo de respuesta

Un parmetro importante en la evaluacin de un RTOS es su tiempo de respuesta. Un RTOS eficaz slo aade una pequea sobrecarga en el tiempo de respuesta mnimo terico del sistema. Los parmetros tpicos que caen en esta categora son:

Interrupt latency, el tiempo desde una peticin de interrupcin y el de interrupcin. Un RTOS puede aadir un poco de sobrecarga en el servicio de interrupcin. La sobrecarga puede ser causada por cdigo adicional introducido por el RTOS en los controladores de interrupcin rutas de cdigo o por zonas crticas RTOS relacionados. Threads fly-back time, el tiempo de un evento de hardware, por lo general una interrupcin y el reinicio de la tarea supone que manejarlo. Tiempo de cambio de contexto, el tiempo necesario para cambiar de forma sincronizada desde el contexto de un hilo en el contexto de otro hilo.

Por supuesto, un RTOS capaz de reaccionar en 2S es mejor que un sistema que reacciona en 10S. Tenga en cuenta que lo que es realmente significativo es el peor valor del caso, si un sistema reacciona en medio en 5S pero, debido a la fluctuacin, puede tener picos de hasta 20S entonces el valor a considerar es 20S.

Jitter

A good RTOS is also characterized by low intrinsic Jitter

Un buen RTOS tambin se caracteriza por una baja fluctuacin de fase intrnseca en el tiempo de respuesta. Intrnseca debido a fluctuacin de fase tambin est determinada por el diseo global del sistema. Algunos de los factores que determinan el comportamiento del sistema en relacin con fluctuacin de fase son:

Tema prioridades de asignacin. Interrumpir asignacin prioridades. La longitud y el nmero de zonas crticas. Las interacciones entre los temas a travs de recursos compartidos protegidos por la exclusin mutua. El uso de la herencia de prioridad u otros algoritmos / estrategias jitter-reductores.

tamao

En un sistema embebido el RTOS es una sobrecarga importante en trminos de memoria ocupada, un RTOS ms compacto es preferible siendo todos los dems parmetros iguales, porque el costo de memoria.

confiabilidad

Hay opciones de diseo que hacen que algunos sistemas intrnsecamente ms fiable que otros. La asignacin dinmica es un buen ejemplo de una opcin de diseo pobre porque tanto falta de fiabilidad y el tiempo de imprevisibilidad respuesta de algunos esquemas de asignacin. Totalmente diseos estticos no tienen esas limitaciones intrnsecas.primitivos de sincronizacin

Variedad de primitivas disponibles es tambin un factor importante a considerar. Tener la herramienta correcta para el trabajo puede reducir el tiempo de desarrollo y, a menudo tambin ayuda a la hora de integrar cdigo externo con el RTOS.

Un buen ejemplo es el TCP / IP stack lwIP, asume un RTOS ofrece semforos con tiempos de espera, si el RTOS no es compatible con semforos y los tiempos de espera, entonces usted tiene un problema y tendr que encontrar una solucin.

77ChibiOS - Caractersticas

El ChibiOS es una opcin fiable, ya que de acuerdo a sus especificaciones responde positivamente a las caractersticas de un buen sistema operativo y ofrece herramientas que facilita la programacin de aplicaciones incluso sin restricciones de tiempo real.

Como funciona un sistema operativo en tiempo real?T1T2TnMensajesColasEventosSemforosKernelSchedulerEl kernel es el cuerpo del SO, contiene todas las funciones y caractersticas del RTOS. El Programador (schedule) es el corazn del SO y decide que tarea debe correr.Las tareas son las trabajadoras del SO y contienen el cdigo de la aplicacin. Los mensajes y las colas son usadas para enviar datos entre tareas. Los eventos y semforos son seales de sincronizacin entre las diferentes tareas.El ncleo de un sistema operativo es el kernel. (Con el api, se puede acceder al kernel y crear tareas).Cada tarea es como si fuera una funcin con su propia pila (privada) y su propio bloque de control (TCB) el cual tiene la informacin del estado de la tarea.El kernel tiene un scheduler (programador), responsable de ejecutar las tareas de acuerdo al mecanismo de asignacin de tareas. Los ms populares son basados en la prioridad (Priority-based) con derecho preferente (preemptive scheduling). Tpicamente las tareas con la misma prioridad, se ejecutan mediante el mtodo de round-robin. El ChibiOs tiene un scheduler basado en prioridad.

80Asignando prioridadesUtilice el menor nmero de niveles de prioridad como sea posible. Esto para reducir la cantidad de cambios de contexto en el sistema.

Asegrese de que la restricciones crticas de tiempo se cumplan en la aplicacin.ChibiOS - ComponentesChibiOS esta internamente divido en varios componentes:Kernel

Port Layer

Hardware Abstraction Layer

Platform Layer

Board Initialization

KernelBloque principal del sistema operativo. Se subdivide en varios componentes

System: Se encarga de la inicializacin.Timers: Timers virtuales y temporizacinScheduler: Todo el mecanismo de sincronizacin se implementa a travs de este subsistema.ThreadsPort LayerEste componente es el responsable de la puesta en marcha del sistema, interrupciones, primitivas de bloqueo/desbloqueo, cambio de contexto y las estructuras relacionadas con interrupcin de cdigoHardware Abstraction Layer (HAL)El HAL es un conjunto de drivers de dispositivos, que se basa en los componentes de la placa para la implementacin de bajo nivel en el hardware especfico.El propsito de este componente es abstraer al usuario del hardware.Arquitectura HAL

Board Initialization LayerEsta capa contiene un conjunto de implementaciones de drivers de dispositivos.Platform LayerEste archivo es usado por el startup del sistema para inicializar la placa.Dependencias

En la imagen puede verse la interdependencia de los compontes antes descriptosExternsSon libreras que se pueden agregar al directorio del sistema operativo para manejo de ms perifricos, como la librera para el manejo de la FAT, el stack TCP/IP, etc.Ejemplos prctico utilizando un RTOS como herramienta de programacin

SISTEMA OPERATIVO RTOSCreacin de threads

Hay dos clases dehilosen ChibiOS / RT:

StaticThreads:Reserva estticamente la memoria en tiempo de compilacin.DynamicThreads:Se realiza la asignacin de memoria en tiempo de ejecucin de un conjunto de memoria o de un banco de memoria (reduce la fiabilidad del sistema).

Creacin de un thread esttico

Para crear un thread esttico se debe usar WORKING_AREA

static WORKING_AREA(myThreadWorkingArea, 128);

En este caso, se reservan 128 bytes de la pila para uso del threadUn thread esttico se puede iniciar mediante la invocacin dechThdCreateStatic ()

Thread *tp = chThdCreateStatic (myThreadWorkingArea, sizeof(myThreadWorkingArea), NORMALPRIO, /* Initial priority. */ myThread, /* Thread function. */ NULL); /* Thread parameter. */Ejemplo, Leds intermitentes utilizando RTOS

Ejercicio: Modificar el ejemplo para hacer titilar todos los leds a distintas frecuenciasComunicacin entre TareasLa comunicacin puede tener la forma de un evento, un semforo (flag), o un mensaje que se enva a otra tarea.

La forma ms bsica de comunicacin es mediante un evento. Un servicio de interrupcin puede enviar un evento a una tarea, algunos SOs tambin pueden enviar un evento a varias tareas.Semforos: Se utilizan para proteger recursos compartidos, por ejemplo, si hay ms de una tarea que necesita escribir/leer en la misma memoria (variable) el uso de un semforo asegura que solamente una tarea va a escribir o leer a la vez.Mensajes: Permite enviar datos a uno o ms tareas. Se implementan como mailbox o queue.

Ejemplo de sincronizacin de tareas con semforos binarios

Toma el recurso 1, ejecuta la tarea.Libera el recurso 2Toma el recurso 2Libera el recurso 1Recurso 2, inicia como tomado.Ejemplo de aplicacin de mensajes

Ejemplo de aplicacin de mensajes

Lnea de comandos por USBInstrucciones por medio de una lnea de texto simple.Generando un COM virtual mediante CDC (Comunication Device Class)

Lnea de comandos por USB

Al conectar el puerto USB modo device se piden instalar driver, utilizar VCP_Setup.zip, driver de ST.100Ejemplo de utilizacin de libreras externas con ChibiOS (Fatfs y Lwip)Por las caractersticas de mensajera y sincronizacin del RTOS es posible utilizar una librera externa como Lwip o Fatfs.

Ejemplo de utilizacin de libreras externas con ChibiOS (Lwip)

Ejemplo de utilizacin de libreras externas con ChibiOS (Lwip)

Ejemplo de utilizacin de libreras externas con ChibiOS (Lwip)

Interactuar con la pgina WebFormularios, delimitados con la etiqueta ... METHOD:POST, enva los datos al agente de procesamiento almacenndolos en el cuerpo del formularioGET, enva los datos agregndolos a la direccin URL y separndolos de la direccin con un signo de interrogacin.ACTION:indica la direccin a la que se enviar la informacin.La etiqueta FORM acta como una especie de contenedor para almacenar elementos que permiten al usuario seleccionar o introducir datos. Todos los datos se enviarn a la direccin URL indicada en el atributo ACTION de la etiqueta FORM, por el mtodo indicado en el atributo METHOD.

Se puede insertar cualquier elemento HTML en una etiqueta FORM (como texto, botones, tablas y enlaces), pero los elementos interactivos son los ms interesantes. Estos elementos interactivos son:

La etiqueta INPUT: Todos los botones y casillas de textoLa etiqueta TEXTAREA: una casilla de textoLa etiqueta SELECT: una lista de opciones mltiples105Interactuar con la pgina Web

Ejercicio: Capturar la siguiente solicitud en el server Web y cambiar el estado de un led

El atributo type se usa para especificar qu tipo de elemento se representa con la etiqueta INPUT. Estos son los valores posibles:checkbox: Las casillas de eleccin pueden adoptar uno de dos estados: checked (seleccionado) o unchecked (no seleccionado). Cuando la casilla es seleccionada, el par nombre/valor se enva al CGI.hidden: Este campo, que el navegador no muestra, es para definir una configuracin nica que se enviar al CGI como par nombre/valor.file: Un campo que permite al usuario especificar una ruta de archivo que lleva al archivo que se enviar con el formulario. Los tipos de archivo que pueden ser enviados deben especificarse utilizando el atributo ACCEPT de la etiqueta FORM.image: Un botn de envo personalizado que aparece cuando se ubica una imagen en la ubicacin definida por el atributo SRC.password: Una casilla de texto donde los caracteres escritos aparecen como asteriscos para camuflar el texto de entrada.radio: Un botn que permite al usuario elegir entre varias opciones. Cada uno de estos botones debe tener el mismo atributo name. El par nombre/valor del botn radio seleccionado se enviar al CGI. Al aplicar el atributo checked para uno de estos botones se definir como seleccionado de forma predeterminada.reset: Un botn de restauracin para quitar todos los elementos en el formulario y restablecer sus valores predeterminados.submit: Un botn de envo para enviar el formulario. El texto en el botn puede definirse usando el atributo value.text: Una casilla de texto para escribir una lnea de texto. El tamao de la casilla puede definirse usando el atributo size y la extensin mxima del texto con el atributo maxlength.

En web.c, funcin http_server_serve ->

Para enteder se puede colocar un break point y observar que solicitud llega cada vez en buf.

if ((buflen >=5) && (strncmp(buf, "GET /", 5) == 0)) { if(strncmp(buf, "GET /index.html?bt_led=1", 24) == 0){ palTogglePad(GPIOG, GPIOG_LED1); } /* Send our HTML page */ netconn_write(conn, http_index_html, sizeof(http_index_html)-1, NETCONN_NOCOPY); }106Ejemplo de utilizacin de libreras externas con ChibiOS (Fatfs)

Ejemplo de utilizacin de libreras externas con ChibiOS (Fatfs)

Ejemplo de utilizacin de libreras externas con ChibiOS (Fatfs)

Wave PlayerServer HTMLLectura SD, escritura DAC

Play, Pause, StopReferenciashttp://www.arm.com/http://cmsis.arm.com/http://www.chibios.org/Basic Concepts for Real Time Operating Systems by Mats Pettersson, IAR SystemsDesarrollo con microcontroladores ARM. Sergio Caprile.

Preguntas?