000144461

-

Upload

harrison-ucros -

Category

Documents

-

view

224 -

download

4

description

Transcript of 000144461

-

UNIVERSIDAD SIMN BOLVAR Decanato de Estudios de Profesionales Coordinacin de Ingeniera Electrnica

DISEO, ELABORACIN E IMPLEMENTACIN DE UN RECTIFICADOR TRIFSICO CONTROLADO MEDIANTE PID DIGITAL COMO ELEMENTO PRIMARIO DE REGULACIN PARA UNA FUENTE

DC DE LABORATORIO DE 15 KW

Por Jorge Luis Unamo Marquez

Sartenejas Septiembre, 2006

-

i

UNIVERSIDAD SIMN BOLVAR Decanato de Estudios de Profesionales Coordinacin de Ingeniera Electrnica

DISEO, ELABORACIN E IMPLEMENTACIN DE UN RECTIFICADOR TRIFSICO CONTROLADO MEDIANTE PID DIGITAL COMO

ELEMENTO PRIMARIO DE REGULACIN PARA UNA FUENTE DC DE LABORATORIO DE 15 KW

Por Jorge Luis Unamo Marquez

Realizado con la Asesora de Julio Walter

PROYECTO DE GRADO Presentado ante la Ilustre Universidad Simn Bolvar

Como requisito parcial para optar al ttulo de Ingeniero Electrnico

Sartenejas, Septiembre de 2008

-

ii

UNIVERSIDAD SIMN BOLVAR Decanato de Estudios de Profesionales Coordinacin de Ingeniera Electrnica

DISEO, ELABORACIN E IMPLEMENTACIN DE UN RECTIFICADOR TRIFSICO CONTROLADO MEDIANTE PID DIGITAL COMO ELEMENTO PRIMARIO DE REGULACIN PARA UNA FUENTE DC DE LABORATORIO

DE 15 KW

PROYECTO DE GRADO PRESENTADO POR JORGE LUIS UNAMO MARQUEZ

CARNET: 9831328

REALIZADO CON LA ASESORA DE JULIO WALTER

RESUMEN Existen necesidades de laboratorio para una fuente DC de muy alta potencia que sin embargo posea buena regulacin y bajo ruido. Para ste tipo de caso siempre ha sido utilizado un elemento lineal de control de la tensin de salida, el inconveniente es que inclusive desde potencias bajas la disipacin del elemento de control se hace prohibitiva, por lo que se usan mtodos alternos de regulacin, tales como control de fase y sistemas conmutados. Estos sistemas adolecen de problemas de regulacin y de ruido. Sin embargo, realizando una combinacin de ambas propuestas (lineal y conmutada) se puede obtener una fuente con baja disipacin de potencia y excelente regulacin. Por ello se ha diseado y construido una fuente DC de 15kW que cumpla con las caractersticas de versatilidad, buena regulacin y bajo ruido. El sistema de control utilizado se basa en un grupo de microcontroladores PICs y CPDLs en configuracin maestro esclavo y un protocolo robusto de comunicacin I2C. Para la adquisicin y procesamiento de los datos experimentales se desarrollo una interfaz grfica usando la ayuda de un software comercial (LabView). La comunicacin entre la fuente y la interfaz esta fundamentada en el estndar RS-232. El desarrollo de un prototipo de una fuente de ste estilo, permite el dominio de la tecnologa envuelta en ella para una futura estandarizacin, y de sta manera explotar al mximo sus ventajas, adems hace de la fuente un producto altamente comercial gracias a sus mltiples cualidades. PALABRAS CLAVES Sistema, medicin, comunicacin, innovacin, eficiencia, transferencia tecnolgica, procesamiento, robusto, disipacin, regulacin, ruido.

Sartenejas, Septiembre de 2008

-

iii

AGRADECIMIENTO Hace algunos aos cuando decid comenzar una carrera universitaria jams pens que sera tan gratificante escribir unas pocas lneas como estas. Este trabajo es producto de muchos altibajos en mi vida y de muchas interacciones con distintas empresas, instituciones y personas. Instituciones tales como Fundacin Instituto de Ingeniera en la que hoy en da trabajo y personas como Julio Walter con el que he establecido una gran amistad; No vale la pena enumerar la cantidad de inconvenientes que se me presentaron a lo largo de esta ardua carrera para poder optar por el ttulo de Ingeniero Electrnico, lo que si es conveniente resaltar son nombres como: Julio Walter Thas Gmez Alexabel Liendo Tomas Ramos Jos Unamo Joel Salazar Nereida Garca Rubn Fernndez Manuel Gonzlez David Madrid Rafael el Manga Jairo Pascuzzo Jess Canales Nidia Goncalves Georman Caldern Entre otras muchas personas que en algn momento me brindaron su apoyo, una sonrisa, una palmada en la espalda, una respuesta acertada, una conversacin liberadora, su paciencia y por que no decirlo tambin sus regaos. A todas esas personas que no mencione y no por eso son menos importantes y a todas las mencionadas aqu les extiendo mi ms sincero e infinito agradecimiento. GRACIAS Pudiese extenderme hojas y hojas de personas, palabras y agradecimientos porque realmente fui muy afortunado al tener a mi alrededor grandes personajes que nunca dudaron de mi y mi capacidad. Pero no puedo terminar ste pequeo agradecimiento sin antes mencionar a mis padres Jorge Unamo y Magaly Marquez, sin ellos nada de esto hubiese sido posible.

-

iv

ndice General

1. Introduccin ....................................................................................... 1

1.1. Planteamiento del problema....................................................................... 1 1.2. Justificacin................................................................................................... 1 1.3. Limitaciones .................................................................................................. 2 1.4. Delimitacin .................................................................................................. 2

2. Cuerpo del Trabajo............................................................................ 3

2.1. Objetivo General .......................................................................................... 3 2.2. Objetivos Especficos.................................................................................... 3 2.3. Hiptesis ........................................................................................................ 3 2.4. Fundamentos Tericos ................................................................................. 4

2.4.1 El SCR....................................................................................................... 4 2.4.2 El Transistor IGBT.................................................................................... 5 2.4.3 Efecto Hall clsico .................................................................................... 6 2.4.4 Voltajes Trifsicos..................................................................................... 7 2.4.5 Rectificador Trifsico Completamente Controlado .................................. 8

2.4.5.1 Sincronizacin de las Seales.....................................................................12 2.4.6 El controlador PID .................................................................................. 15 2.4.7 Reguladores de Tensin .......................................................................... 18

2.4.7.1 Reguladores Conmutados ...........................................................................18 2.4.7.2 Reguladores Lineales..................................................................................19 2.4.7.3 Regulador de Tensin en Serie ...................................................................19

2.4.8 Comunicacin y Transmisin de Datos .................................................. 20 2.4.8.1 Bus I2C.......................................................................................................20 2.4.8.2 Protocolo Serial ..........................................................................................23

3. Sistema Adjudicado ......................................................................... 26

3.1. Presentacin ................................................................................................ 26 3.2. Esquema de la Fuente DC.......................................................................... 26

3.2.1 El Transformador de Potencia................................................................. 27 3.2.2 Modulo Rectificador y Filtro LC ............................................................ 28 3.2.3 Tarjetas de Control, Visualizadora y Fuente Conmutada ....................... 30

3.2.3.1 Tarjeta de Control .......................................................................................31 3.2.3.2 La Tarjeta Visualizadora.............................................................................32

3.2.4 El Transistor de Potencia IGBT .............................................................. 34

-

v

4. Culminacin del Chasis y Cableado............................................... 36

4.1. Presentacin ................................................................................................ 36 4.2. Piezas y Partes Faltantes............................................................................ 36

4.2.1 Rectificacin y Filtrado........................................................................... 36 4.2.2 Visualizacin........................................................................................... 37 4.2.3 Control..................................................................................................... 39 4.2.4 Chasis General......................................................................................... 40 4.2.5 Cableado Preliminar ................................................................................ 41

5. Resultados Experimentales y Consideraciones tericas............... 46

5.1. Presentacin ................................................................................................ 46 5.2. Rectificacin Trifsica................................................................................ 46

5.2.1 Acondicionamiento de las Seales de Disparo ....................................... 46 5.2.2 Sincronizacin de los Disparos ............................................................... 48 5.2.3 Duracin del Pulso de Disparo y Observacin de la Onda Rectificada .. 53

5.3. El PID Discreto ........................................................................................... 60 5.3.1 Caracterizacin del Rectificador ............................................................. 60 5.3.2 Modelo Matemtico del Filtro LC y Entonacin Terica del PID.......... 63 5.3.3 Implementacin del Controlador PID Discreto....................................... 66

5.4. Regulacin Lineal ....................................................................................... 73 5.4.1 Modificacin en el Cdigo Fuente del PIC............................................. 73

5.4.1.1 Modificacin de La consigna del PID discreto...........................................73 5.4.1.2 Mejoramiento de la Comunicacin Serial ..................................................74 5.4.1.3 Almacenamiento en la EEPROM del PIC ..................................................76

5.4.2 Ampliacin de la Interfaz Grfica ........................................................... 76 5.4.3 Pruebas Preliminares de Regulacin Lineal............................................ 81

5.4.3.1 Calibracin de la Fuente .............................................................................84 5.4.4 Pruebas Finales de la Fuente ................................................................... 87

5.4.4.1 Regulacin de Carga...................................................................................90 5.4.4.2 Mxima Potencia Entregada .......................................................................93

6. Conclusiones ..................................................................................... 95

7. Recomendaciones ............................................................................. 96

7.1. Captura de la Consigna de Voltaje ........................................................... 96 7.2. Control de Potencia .................................................................................... 96 7.3. Diferencia de Voltaje entre los Extremos del Regulador, Dinmica ..... 97

8. Bibliografa ....................................................................................... 99

-

vi

9. Apndice.......................................................................................... 100

9.1. Cdigo Inicial del PIC de Control........................................................... 100 9.2. Cdigo Final del PIC de Control............................................................. 101 9.3. Tablas de Calibracin de los Instrumento ............................................. 109 9.4. Hoja Tcnica del Codificador ptico ..................................................... 110

-

vii

ndice de Tablas y Figuras

Fig. 2.1: Esquema bsico del SCR y su respectivo smbolo .......................................................4

Fig. 2.2: Smbolo del IGBT: Gate o puerta (G), colector (C) y emisor (E) y su circuito equivalente...................................................................................................................................5

Fig. 2.3: Seccin de un IGBT......................................................................................................5

Fig. 2.4: Efecto Hall clsico. .......................................................................................................6

Fig. 2.5: Ejemplo de generacin de energa trifsica. .................................................................8

Fig. 2.6: Circuito de un puente rectificador de 3 fases completamente controlado. ...................8

Fig. 2.7: Voltajes trifsicos..........................................................................................................9

Fig. 2.8: Ejemplo de un rectificador trifsico completamente, detalle de la forma de onda del voltaje de salida segn el ngulo de disparo y promedio del voltaje (DC)............................11 Fig. 2.9: DC de salida, voltaje en funcin del ngulo de disparo para un rectificador con fuente de voltaje como parte de la carga. .............................................................................................12

Fig. 2.10: Defasaje del voltaje de lnea RB con respecto a los 3 voltajes de fase.....................13

Fig. 2.11: Representacin fasorial de los voltajes de fase y los voltajes de lnea. ....................13

Fig. 2.12: Interconexin de los transformadores de control para el circuito de disparo. ..........14

Fig. 2.13: Seales de disparo con sus respectivas referencias para =0 ...................................14 Fig. 2.14: Seales de disparo con sus respectivas referencias para =60. ................................15 Fig. 2.15: Diagrama de bloques de un regulador de tensin lineal ..........................................19

Fig. 2.16: a) Regulador de tensin en serie simple. b) Regulador de tensin en serie basado en un AO ........................................................................................................................................20

Fig. 2.17: Estructura de un BUS I2C.........................................................................................21

Fig. 3.1: Esquema bsico de la fuente con control independiente entre el rectificador y el regulador....................................................................................................................................26

Fig. 3.2: Configuracin del transformador de potencia.............................................................27

-

viii

Fig. 3.3: Detalle del transformador y parte del chasis ...............................................................28

Fig. 3.4: Empaque del SKKT91/04 y su respectivo smbolo ....................................................29

Fig. 3.5: Circuito rectificador y filtro LC ..................................................................................29

Fig. 3.6: Bobina del filtro LC 1,4mH @ 150Amp ....................................................................30

Fig. 3.7 Detalle del mdulo metlico, los tiristores y el banco de condensadores ....................30

Fig. 3.8: Tarjetas de Control, Visualizadora y Fuente Conmutada, entregadas. .......................31

Fig. 3.10: Diagrama Circuital de la Tarjeta Visualizadora........................................................33

Fig. 3.11: IGBT SKM400GA124D y su smbolo......................................................................34

Fig. 3.12: Detalle del disipador y sobre ste el mdulo rectificador, el transistor de potencia y el ventilador. ..............................................................................................................................35

Fig. 4.1: Barras perforas de cobre utilizadas para la interconexin del banco de condensadores y los 3 pares de tiristores ...........................................................................................................36

Fig. 4.2: Mdulo de tiristores puenteados con las barras de cobre............................................37

Fig. 4.3: Banco de condensadores conectados en paralelo con el par de barras de cobre.........37

Fig. 4.4: Diseo del panel frontal y un soporte necesario para fijar el teclado .........................38

Fig. 4.5: Panel listo y ensamblado.............................................................................................38

Fig. 4.6: Sensor de corriente CSLA2CF....................................................................................39

Fig. 4.7: Diseo en 3D de las piezas necesarias para la medicin de corriente ........................39

Fig. 4.8: Detalle de el sensor de corriente, la barra de cobre con sus respectivas bases y las conexiones trmicas al disipador...............................................................................................40

Fig. 4.9: Diseo de la carcasa completa de la fuente y bornera ................................................40

Fig. 4.10: a) Detalle de las borneras ya fabricadas b) Carcasa completa del chasis..................41

Fig. 4.11: Esquema del encendido/apagado de seguridad de la fuente .....................................42

Fig. 4.12: a) Chasis ensamblado y pintado ntese el panel frontal. b) Contactor de enclavamiento para el encendido y apagado de la fuente..........................................................43

Fig. 4.13: a) Fuente completamente cableada. b) Parte trasera del panel frontal......................45

Fig. 4.14: Detalle de la interconexin de la tarjeta de control...................................................45

-

ix

Fig. 5.1: Disparo de los tiristores 1 y 2 luego de colocar la resistencia de 100......................47 Fig. 5.2: Detalle del acondicionamiento de la seal de disparo. ...............................................47

Fig. 5.3: a) Pulso de Disparo T1 vs RT. b) Pulso de Disparo T2 vs RT. c) Pulso de Disparo T3 vs RT. d) Pulso de Disparo T4 vs RT. e) Pulso de Disparo T5 vs RT. f) Pulso de Disparo T6 vs RT ..............................................................................................................................................49

Fig. 5.4: Circuito del rectificador trifsico simulado.................................................................50

Fig. 5.5: a) Simulacin de las seales de referencia RT, TS y SR. b) Seales RT, TS y SR obtenidas en la tarjeta de control. ..............................................................................................51

Fig. 5.6: Seal de referencia RT anloga y RT digital desfasada 180. ....................................52 Fig. 5.7: Seales de disparo T1 y T2 con respecto a la fase R para un =0. ...........................52 Fig. 5.8: De izquierda a derecha: Tarjeta de adquisicin de datos y extensora utilizadas ........54

Fig. 5.9: Cdigo en LabVIEW para registrar las seales de referencia y disparo.....................54

Fig. 5.10: Datos logrados con la tarjeta de adquisicin de datos 779068-01: a) Seales de referencia analgicas, b) Seales de referencia digitales y c) Pulsos de disparos.....................55

Fig. 5.11: Barrido del pulso de disparo T1 vs. Voltaje rectificado. ..........................................56

Fig. 5.12: Barrido del pulso de disparo T1 vs. Voltaje rectificado, para distintos valores de (cdigo FPGA corregido). .........................................................................................................58

Fig. 5.13: Detalle de la zona de conmutacin en la seal rectificada con respecto al tren de pulso de disparo T1. ..................................................................................................................59

Fig. 5.14: Forma de onda de la seal rectificada una vez conectado el filtro LC, para distintos valores del ngulo de disparo .................................................................................................59 Fig. 5.15: Grfica de voltaje rectificado vs ngulo de disparo (formato 8bits). ........................61

Fig. 5.16: Circuito del filtro LC del rectificador. ......................................................................63

Fig. 5.17: Proceso simulado para encontrar las constantes del controlador PID.......................64

Fig. 5.18: Detalle del diagrama de polos y cero del sistema, diagrama de fase, diagrama de magnitud y respuesta al escaln para el compensador preliminar.............................................65

Fig. 5.18: Detalle del diagrama de polos y cero del sistema, diagrama de fase, diagrama de magnitud y respuesta al escaln para el compensador ya entonado..........................................66

Fig. 5.19: Respuesta del rectificador ante varias consignas de voltaje (valores medidos a travs de la tarjeta de control). .................................................................................................69

-

x

Fig. 5.20: Detalle del sobrepico en la respuesta del controlador (valores medidos a travs de la tarjeta de control). .....................................................................................................................69

Fig. 5.21: Referencia de la oscilacin y el transitorio antes de recuperarse la seal (valores medidos a travs de la tarjeta de control). ................................................................................70

Fig. 5.22: Ensayo final del rectificador controlado por el PID discreto (valores medidos a travs de la tarjeta de control). .................................................................................................71

Fig. 5.23: Detalle de la respuesta frente al escaln, del ensayo final en el rectificador (valores medidos a travs de la tarjeta de control). ................................................................................71

Fig. 5.24: Referencia de la respuesta del rectificador, ante disminuciones bruscas del set de voltaje (valores medidos a travs de la tarjeta de control). ......................................................72

Fig. 5.25: Esquema bsico de la regulacin propuesta..............................................................74

Fig. 5.26: Formato de una de las tramas de envo de datos a la PC. .........................................74

Fig. 5.26: Trama de envo de las constantes del controlador PID a la PC. ...............................75

Fig. 5.27: Detalle de una parte de la interfaz grfica modificada..............................................77

Fig. 5.28: Panel frontal de la interfaz grfica mejorada. ...........................................................78

Fig. 5.29: Parte del cdigo implementado, para la interfaz grfica modificada. Estado 5: recepcin y visualizacin de los valores de la fuente................................................................79

Fig. 5.30: Parte del cdigo de la mquina de estados. Estado 6: Recepcin de constantes. .....80

Fig. 5.31: Prueba preliminar de regulacin (valores medidos a travs de la tarjeta de control)....................................................................................................................................................81

Fig. 5.32: Lazo dual de control para el transistor de potencia...................................................82

Fig. 5.33: Respuesta del regulador, luego de la entonacin anloga preliminar (valores medidos a travs de la tarjeta de control). ................................................................................82

Fig. 5.34: Detalle de un ensayo preliminar del regulador lineal (valores medidos a travs de la tarjeta de control). .....................................................................................................................83

Fig. 5.35: Calibracin de la medicin de la corriente de salida. ...............................................86

Fig. 5.36: Calibracin del set en el voltaje de salida. ................................................................86

Fig. 5.38: Prueba final de la fuente, con picos de potencia en el elemento de paso..................87

Fig. 5.39: Detalle del pico de potencia en el elemento de paso.................................................88

-

xi

Fig. 5.40: Prueba de la fuente en modo: fuente de corriente. ....................................................89

Fig. 5.41: Ensayo preliminar de regulacin de carga. ...............................................................91

Fig. 5.42: Detalle de la regulacin de lnea para voltajes altos del rectificador........................92

Fig. 5.43: Prueba de la fuente DC entregando 12,5 kW............................................................93

Fig. 5.44: Prueba de la fuente DC entregando 13,4 kW............................................................94

Fig. 7.1: Control de potencia para proteger al elemento regulador. ..........................................97

Fig. 7.2: Diferencia de voltaje dinmica....................................................................................98

-

xii

Tabla 2.1: Par de diodos en conduccin segn el ngulo , s se sustituyeran los tiristores de la figura 2.6 por diodos..................................................................................................................10

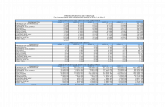

Tabla 2.2: Par de SCRs en conduccin segn el ngulo de disparo . ....................................11 Tabla 5.1: Valores medidos en el rectificador, que reflejan la relacin entre el ngulo de disparo () y el voltaje en el mismo..........................................................................................60 Tabla 5.2: Valores enteros calculados del controlador PID y su correspondiente .................62 Tabla 5.3: Tabla para la calibracin de la fuente (valores medidos). ........................................85

Tabla 9.1: Calibracin de los instrumentos. ............................................................................109

-

xiii

Lista de Smbolos y Abreviaturas

: Frecuencia de la red (en rad/s).

Hz : Frecuencia de la red en herzios.

Vrms: Root mean Square (raz media cuadrtica).

AC: Altern current (corriente Alterna).

DC: Direct Current (corriente directa).

SCR: Silicon controller rectifier (rectificador controlado de silicio).

PNPN: Positivo negativo positivo negativo.

BJT: Bipolar junction transistor (transistor bipolar).

FET: Field effect transistor (transistor de efecto de campo).

J0: Densidad de corriente en la superficie de la pieza.

P0: Potencia disipada en la superficie de la pieza.

L: Inductancia del inductor de calentamiento.

C: Condensador para compensar la potencia reactiva de L.

Zc: Impedancia caracterstica.

s: Variable de la Transformada de Laplace.

Z(s): Funcin impedancia.

Q: Factor de calidad de la bobina a la frecuencia de resonancia.

IGBT: Insulated Gate Bipolar Transistor.

P, W: Potencia de salida del inversor serie.

V: Tensin soportada por el conmutador.

I: Corriente por el conmutador.

PID: Red de compensacin Proporcional Integro-Diferencial

-

1

1. Introduccin

1.1. Planteamiento del problema

Gracias al desarrollo tecnolgico tan acelerado que ha venido experimentando el

mundo en stas ultimas dcadas, la sociedad venezolana se ha visto en la imperiosa

necesidad de formar cada vez ms profesionales en el rea tecnolgica, capaces de

investigar y desarrollar proyectos de mediana y gran envergadura.

El estado venezolano en el afn de no quedarse atrs ante el desarrollo

tecnolgico global invierte grandes esfuerzos en instituciones dedicadas a la formacin de

profesionales tcnicos y de investigacin, por medio de escuelas tcnicas, politcnicos,

universidades, etc. Adems de instituciones como el IVIC (Instituto Venezolano de

Investigaciones Cientficas), IDEA (Instituto de Estudios Avanzados) y la FII (Fundacin

Instituto de Ingeniera) las cules brindan al estado venezolano servicios tecnolgicos,

donde se puede destacar como una de las primordiales caractersticas la transferencia de

tecnologa.

Regularmente en las diversas instituciones antes mencionadas existe la necesidad

de fuentes DC regulables para laboratorio, que manejen altos niveles de potencia con

buenos mrgenes de regulacin y bajo ruido. Lo que se estila en ste tipo de casos es la

utilizacin de un dispositivo lineal para el control del voltaje de salida, pero el

inconveniente surge cuando an a bajos niveles potencias la disipacin en el elemento de

paso se hace prohibitiva.

1.2. Justificacin

Claro esta que en Venezuela podemos adquirir a travs de importaciones fuentes

DC de laboratorio de altsima potencia y bajo ruido. Pero a un alto precio y sin

transferencia de tecnologa. En este sentido y enmarcado en las polticas de estado,

instituciones como La Fundacin Instituto de Ingeniera (FII) apuesta directamente a la

fabricacin de productos nacionales donde el conocimiento, el dominio de la tecnologa,

la experiencia y la investigacin reposen en nuestros profesionales.

En estos momentos la FII esta desarrollando un proyecto de ndole interno cuyo

objetivo macro es incursionar de manera profunda en un campo que tiene mucho auge

desde hace algn tiempo; el cul es, el de las energas alternativas. Para as ms

-

2

adelante contar con la experiencia y las herramientas necesarias para brindar un servicio

de calidad a una gran diversidad de clientes as como tambin apoyar y transferir

conocimientos a comunidades de bajos recursos y difcil acceso por medio de planes de

accin nacional.

Una de las fases del proyecto es el diseo, implementacin y desarrollo de

inversores de media potencia (hasta 35 kVA), como bien sabemos inversores de este tipo

necesitaran de un gran banco de bateras para su funcionamiento. Para efectos de

pruebas experimentales en el desarrollo de un prototipo de un inversor de este estilo, no

es prctico ni rentable disponer de un gran banco de bateras, sobre todo por el

mantenimiento, el proceso de carga y descarga y el costo del mismo la mejor solucin es

utilizar los recursos disponibles, en este caso la red trifsica convencional.

Aqu es donde entra en relacin directa la elaboracin de un convertidor AC-DC o

si se quiere llamarlo, una fuente de poder DC regulable para sustituir esos grandes

bancos de bateras por un solo dispositivo capaz de suministrar esos niveles de potencia y

que adems es til en muchas otras aplicaciones. El hecho de que sta fuente tenga

muchas otras aplicaciones, su costo de elaboracin sea relativamente econmico en

comparacin con un dispositivo similar importado y que adems es altamente eficiente y

til; hace de ella un producto altamente comercializable.

1.3. Limitaciones

Debido a su carcter de prototipo, ste proyecto estar sujeto a cambios de forma

y de fondo, que no estn contemplados en un principio sino que se irn presentado a

travs del desarrollo del mismo. Esta fuente no cuenta con un software ni una interfaz

grfica que permita el anlisis de sus parmetros en detalle, la elaboracin de un

controlador PID digital para un rectificador controlado no contempla dicho software, ni

todas las mejoras posibles que se le puedan efectuar al sistema para su posible

comercializacin.

1.4. Delimitacin

El presente proyecto ser ejecutado en la Fundacin Instituto de Ingeniera,

especficamente el departamento de Ingeniera Elctrica y Sistemas en un lapso de 24

semanas, al final de dicho tiempo la fuente estar totalmente operativa con las mejoras y

cambios que hayan sido necesarios debidamente implementados.

-

3

2. Cuerpo del Trabajo

2.1. Objetivo General

Disear, elaborar e implementar un Rectificador Trifsico controlado mediante un

control discreto (PID digital), como elemento primario de regulacin para una fuente DC

de laboratorio de 15 kW.

2.2. Objetivos Especficos Revisar la bibliografa referente de todos los tpicos referentes a rectificacin trifsica,

transistores de potencia en especial IGBT, tiristores de potencia y todo el material

suministrado por el Profesor Julio Walter.

Culminar el chasis: diseo y fabricacin de piezas diversas para el correcto funcionamiento de la fuente.

Interconectar y cablear los circuitos impresos y dispositivos que conforman todo el sistema: banco de condensadores, banco de tiristores, bobina de choque y

transformador de potencia.

Realizar de pruebas preliminares de los circuitos impresos: comunicacin entre ellos, correcto funcionamiento, primeros ensayos de rectificacin y de control manual.

Disear e implementar el control PID discreto. Ejecutar las pruebas preliminares de autorregulacin regidas por el controlador PID

discreto.

Ejecutar las pruebas finales de regulacin con el elemento de paso integrado para validar su funcionamiento.

Elaborar el manual de usuario para asegurar el buen funcionamiento de la fuente. 2.3. Hiptesis

Es posible crear una fuente DC de laboratorio de 15kW utilizando como elemento

de paso regulador un transistor de potencia, operado en la zona lineal y siendo regido su

entorno por controladores PIDs anlogos y discretos.

-

4

2.4. Fundamentos Tericos

Debido al carcter experimental de ste proyecto los fundamentos tericos a

abarcar son muchos, as que solamente se describirn a continuacin los ms

importantes.

2.4.1 El SCR

El rectificador controlado de silicio (en ingls SCR: Silicon Controlled Rectifier) es

un dispositivo de estado slido formado por cuatro capas de material semiconductor con

estructura PNPN o bien NPNP. El nombre proviene de la unin de Tiratrn (tyratron) y

Transistor. La figura 2.1 muestra el esquema del SCR.

Fig. 2.1: Esquema bsico del SCR y su respectivo smbolo

Un SCR posee tres conexiones: nodo, ctodo y puerta. La puerta es la encargada

de controlar el paso de corriente entre el nodo y el ctodo. Funciona bsicamente como

un diodo rectificador controlado, permitiendo circular la corriente en un solo sentido.

Mientras no se aplique ninguna tensin en la puerta del SCR no se inicia la conduccin y

en el instante en que se aplique dicha tensin, el tiristor comienza a conducir. Una vez

arrancado, podemos anular la tensin de puerta y el tiristor continuar conduciendo hasta

que la corriente de carga disminuya por debajo de la corriente de mantenimiento.

Trabajando en corriente alterna el SCR se desactiva en cada alternancia o semiciclo.

Cuando se produce una variacin brusca de tensin entre nodo y ctodo de un tiristor,

ste puede dispararse y entrar en conduccin an sin corriente de puerta. Por ello se da

como caracterstica la tasa mxima de subida de tensin que permite mantener

bloqueado el SCR. Este efecto se produce debido al condensador parsito existente entre

la puerta y el nodo. Los SCR se utilizan en aplicaciones de electrnica de potencia y de

control. Podramos decir que un SCR funciona como un interruptor electrnico.

-

5

2.4.2 El Transistor IGBT

El transistor bipolar de puerta aislada (IGBT, del ingls Insulated Gate Bipolar

Transistor) es un dispositivo semiconductor que generalmente se aplica como interruptor

controlado en circuitos de electrnica de potencia. La figura 2.2 muestra el esquema del

transistor IGBT.

Fig. 2.2: Smbolo del IGBT: Gate o puerta (G), colector (C) y emisor (E) y su circuito

equivalente

Este dispositivo posee la caractersticas de las seales de puerta de los transistores

de efecto campo con la capacidad de alta corriente y bajo voltaje de saturacin del

transistor bipolar, combinando una puerta aislada FET para la entrada de control y un

transistor bipolar como interruptor en un solo dispositivo. El circuito de excitacin del

IGBT es como el del MOSFET, mientras que las caractersticas de conduccin son como

las del BJT. Los transistores IGBT han permitido desarrollos, hasta hace relativamente

poco tiempo, no viables, en particular en los variadores de frecuencia as como en las

aplicaciones en maquinas elctricas y convertidores de potencia que nos acompaan cada

da y por todas partes, sin que seamos particularmente concientes de eso: automvil,

tren, metro, autobs, avin, barco, ascensor, electrodomsticos, televisin, etc. En la

figura 2.3 se puede ver la seccin de un IGBT.

Fig. 2.3: Seccin de un IGBT

-

6

El IGBT es adecuado para velocidades de conmutacin de hasta 20 kHz y ha

sustituido al BJT en muchas aplicaciones. Es usado en aplicaciones de altas y medias

energas como fuente conmutada, control de la traccin en motores y cocinas de

induccin. Grandes mdulos de IGBT que consisten en muchos dispositivos colocados en

paralelo, pueden manejar altas corrientes, del orden de miles de amperios con voltajes de

bloqueo de hasta 6.000 voltios.

Se puede concebir el IGBT como un Darlington hibrido, tiene la capacidad de

manejo de corriente de un bipolar pero no requiere de la corriente de base para

mantenerse en conduccin. Sin embargo las corrientes transitorias de conmutacin de la

base pueden ser igualmente altas. En aplicaciones de electrnica de potencia es el

intermedio entre los tiristores y los mosfets. Maneja ms potencia que los segundos

siendo ms lento que ellos y lo inverso respecto a los primeros.

2.4.3 Efecto Hall clsico

Cuando por un material conductor o semiconductor, circula una corriente elctrica,

y estando este mismo material en el seno de un campo magntico, se comprueba que

aparece una fuerza magntica en los portadores de carga que los reagrupa dentro del

material, esto es, los portadores de carga se desvan y agrupan a un lado del material

conductor o semiconductor, apareciendo as un campo elctrico perpendicular al campo

magntico y al propio campo elctrico generado por la batera. Este campo elctrico es el

denominado campo Hall, y ligado a l aparece la tensin Hall, que se puede medir

mediante un voltmetro.

Fig. 2.4: Efecto Hall clsico.

-

7

En el caso de la figura 2.4, tenemos una barra de un material desconocido y

queremos saber cuales son sus portadores de carga. Para ello, mediante una batera

hacemos circular por la barra una corriente elctrica. Una vez hecho esto, introducimos la

barra en el seno de un campo magntico uniforme y perpendicular a la tableta.

Aparecer entonces una fuerza magntica sobre los portadores de carga, que

tender a agruparlos a un lado de la barra, apareciendo de este modo una tensin Hall y

un campo elctrico Hall entre ambos lados de la barra. Dependiendo de si la lectura del

voltmetro es positiva o negativa, y conociendo el sentido del campo magntico y del

campo elctrico originado por la batera, se puede deducir si los portadores de carga de la

barra de material desconocido son las cargas positivas o las negativas.

2.4.4 Voltajes Trifsicos

La generacin y transmisin de potencias elctricas son ms eficientes en sistemas

polifsicos que emplean combinaciones de dos, tres o ms voltajes sinusoidales. Adems

los circuitos y las maquinas polifsicas poseen ciertas ventajas nicas. Por ejemplo, la

potencia transmitida en un circuito trifsico es constante o independiente del tiempo en

vez de pulsante, como en un circuito monofsico. As mismo, los motores trifsicos

arrancan y funcionan mucho mejor que los monofsicos. La forma ms comn de un

sistema polifsico utiliza tres voltajes balanceados de igual magnitud y desfasados en 120

grados.

Un generador de AC elemental consta de un magneto giratorio y un devanado fijo.

Las vueltas del devanado se distribuyen por la periferia de la mquina. El voltaje

generado en cada espira del devanado esta ligeramente desfasado del generado por el

ms prximo, debido a que la densidad mxima de flujo magntico la corta un instante

antes o despus. Si el primer devanado se continuara alrededor de la maquina, el voltaje

generado en la ltima espira estara desfasado 180 grados de la primera y se cancelaran

sin ningn efecto til. Por esta razn, un devanado se distribuye comnmente en no ms

de un tercio de la periferia; los otros dos tercios se pueden ocupar con dos devanados

ms, usados para generar otros dos voltajes similares.

Un circuito trifsico genera distribuye y utiliza energa en forma de tres voltajes,

iguales en magnitud y simtricos en fase. Las tres partes similares de un sistema trifsico

se llaman fases. Como el voltaje en la fase A alcanza su mximo primero, seguido por la

fase B y despus por la C se dice que la rotacin de fases es ABC. Esta es una convencin

-

8

arbitraria; en cualquier generador, la rotacin de fases puede invertirse, si se invierte el

sentido de rotacin. La figura 2.5 muestra un ejemplo de generacin trifsica.

Fig. 2.5: Ejemplo de generacin de energa trifsica.

2.4.5 Rectificador Trifsico Completamente Controlado

El funcionamiento de un puente rectificador de 3 fases completamente controlado

se describe en esta parte. Un puente rectificador trifsico totalmente controlado puede

ser construido utilizando seis tiristores o SCRs como se muestra a continuacin en la

figura 2.6.

Fig. 2.6: Circuito de un puente rectificador de 3 fases completamente controlado.

El circuito puente rectificador de tres fases consta de tres ramas, cada una de ellas

conectada a uno de los tres voltajes de fase. Alternativamente, se puede observar que el

puente tiene dos mitades de circuito, el medio positivo consistente en los SCRs S1, S3 y

S5 y el medio negativo consistente de los SCRs S2, S 4 y S 6. En cualquier momento,

un SCR de cada mitad esta encendido cuando hay corriente elctrica siempre y cuando

-

9

exista el pulso de disparo adecuado para el dispositivo. Si la secuencia de fases de la

fuente es RYB, los SCRS se activan en la secuencia S1, S2, S3, S4, S5, S6, S1 y as

sucesivamente. Los tres voltajes de fase varan segn se indica La figura 2.7.

Fig. 2.7: Voltajes trifsicos.

Los tres voltajes de fase se definen como se muestra a continuacin:

( ) ( ) SinEVR *= (2.1) ( ) ( )= 120* SinEVY (2.2) ( ) ( )+= 120* SinEVB (2.3)

Se puede observar que la tensin de fase R es la ms alta de los tres voltajes de

fase cuando est en el rango de 30 a 150. Tambin puede verse que la tensin de fase Y es el ms alto de los tres voltajes de fase cuando est en el rango de 150 a 270 y que la tensin de la fase B es la ms alta de los tres voltajes de fase cuando est en el rango de 270 a 390 o 30 en el siguiente ciclo. Tambin se observa que la

primera tensin de fase es la ms baja de los tres voltajes de fase cuando est en el rango de 210 a 330. Igualmente la tensin fase Y es la ms baja de los tres voltajes de

fase cuando est en el rango de 330 a 450 o 90 en el siguiente ciclo, y que la fase B es la ms baja de voltaje cuando est en el rango de 90 hasta 210. Si se utilizan diodos, diodo el D1, en lugar del SCR1 conducira a partir de 30 a 150, el diodo D3

conducira de 150 a 270 y el diodo D5 de 270 a 390 o 30 en el siguiente semiciclo.

De la misma manera, el diodo D4 conducir a partir de 210 a 330, el diodo D6 de

330 a 450 o 90 en el siguiente ciclo, y el diodo D2 conducir a partir de 90 hasta

-

10

210 . El bus positivo de la tensin de salida del puente est conectado a la parte alta del

conjunto de las tres fases, y la parte negativa del bus de la tensin de salida a la parte

baja del conjunto. En cualquier instante del barrido del ngulo , existen cambios de perodos en que el flujo de corriente de un diodo se transfiere a otro, slo uno de los

siguientes pares se lleva a cabo en determinado momento. La tabla 2.1 muestra el par

de diodos en conduccin.

Periodo, rango de Par de diodos en conduccin

30 a 90o D1 y D6

90o a 150o D1 y D2

150o a 210o D2 y D3

210o a 270o D3 y D4

270o a 330o D4 y D5

330o a 360o y 0o a 30o D5 y D6

Tabla 2.1: Par de diodos en conduccin segn el ngulo , s se sustituyeran los tiristores de la figura 2.6 por diodos.

Si se utilizan SCRs, como muestra la figura 2.6 su conduccin puede ser

retrasada por la eleccin del ngulo de disparo deseado. Cuando el SCR se dispara a 0

del ngulo de disparo , la salida del puente rectificador sera la misma que la del circuito con diodos. Por ejemplo, se ve que D1 comienza a conducir slo despus que =30. De hecho, se puede empezar la conduccin slo despus de =30, ya que antes de =30 el diodo est polarizado en inverso. La polarizacin a travs de D1 viene a ser cero cuando

=30 y el diodo D1 comienza a polarizarse en directa slo despus de =30. Cuando ( ) ( ) SinEVR *= , el diodo D1 est inversamente polarizado antes de =30 y est

directamente polarizado para >30 . Cuando el ngulo de disparo de los SCRs es cero grado, S1 se activa cuando =30. Esto significa que si se quiere una sincronizacin de la seal de disparo que se necesita para activar S1, la seal de voltaje ( ) ( ) SinEVR *=

-

11

debera estar desfasada por 30 y si el ngulo de disparo es , S1 se activa cuando = +30. Dado que la conduccin es continua, la tabla siguiente presenta el par SCR en conduccin en cualquier instante. La figura 2.8 muestra un ejemplo de rectificador

trifsico completamente controlado y la 2.9 el voltaje DC de salida del mismo.

Perodo, rango de Par de SCRs en conduccin

+ 30 o a + 90o S 1 y S 6

+ 90o a + 150o S 1 y S 2

+ 150o a + 210o S 2 y S 3

+ 210o a + 270o S 3 y S 4

+ 270o a + 330o S 4 y S 5

+ 330o a + 360o y + 0o a + 30o S 5 y S 6

Tabla 2.2: Par de SCRs en conduccin segn el ngulo de disparo .

Fig. 2.8: Ejemplo de un rectificador trifsico completamente, detalle de la forma de onda del voltaje de salida segn el ngulo de disparo y promedio del voltaje (DC).

-

12

Fig. 2.9: DC de salida, voltaje en funcin del ngulo de disparo para un rectificador con

fuente de voltaje como parte de la carga.

2.4.5.1 Sincronizacin de las Seales

Para variar la tensin de salida, es necesario variar el ngulo de disparo y para

realizar esto ltimo, una tcnica de uso comn es establecer una sincronizacin de la

seal para cada SCR. Se ha visto que el grado cero del ngulo de disparo se produce 30

grados despus del cero de cruce de la respectiva fase de tensin. Si la sincronizacin de

la seal va a ser una seal senoidal, existe un retraso de 30 con las respectivas fases.

Cuando las 3 fases de la fuente de suministro estn conectadas en estrella y el

rectificador est conectado, el voltaje de la lnea y las tensiones de fase tienen 30

desfase entre ellos, como se muestra en la figura 2.10.

El voltaje de lnea tambin puede obtenerse matemticamente como:

( ) ( ) ( ) BRRB VV = V ( ) ( ) ( )+ 120** SinESinE = VRB

( ) ( ) ( ) ( ) CosESinESinE = VRB *2*3*

2*

( ) ( ) 30**3 SinE = VRB (2.4)

-

13

Fig. 2.10: Defasaje del voltaje de lnea RB con respecto a los 3 voltajes de fase.

Fig. 2.11: Representacin fasorial de los voltajes de fase y los voltajes de lnea.

Este retardo en el voltaje de lnea de la fase RB es de 30o y tiene una amplitud que

es 1,732 veces la amplitud de la tensin fase. La sincronizacin de la seal para S1 se

puede obtener sobre la base del voltaje de lnea VRB y La sincronizacin de las seales

para los otros SCR se puede obtener de manera similar. Para obtener la sincronizacin de

las seales, se pueden utilizar tres transformadores de control, con los devanados

primarios conectados en delta y los secundarios en estrella, como se muestra en la figura

2.12.

-

14

Fig. 2.12: Interconexin de los transformadores de control para el circuito de disparo.

Para S1, el voltaje VS1 se utiliza como la seal de sincronizacin de tensin, VS2 se

utiliza como seal para la sincronizacin del S2 y as sucesivamente. Se pueden ver las

seales de disparo como 3 pares de seales VS63, VS25 y VS14 donde las seales en cada

par estn desfasadas 180, a su vez las referencias de stas seales de disparo estn desfasadas por 120, en las figuras 2.13 y 2.14 se pueden ver las 6 seales de disparo para distintos ngulos de disparo, cada una dibujada con el color correspondiente a su

referencia, as mismo se puede observar el defasaje de 180 entre los pares de seales quedando como resultado las seis seales de disparo separadas entre si por 60 y describiendo la secuencia expuesta en la parte 2.4.2 de encendido de los tiristores S1, S2,

S3, S4, S5, S6.

Fig. 2.13: Seales de disparo con sus respectivas referencias para =0

-

15

Fig. 2.14: Seales de disparo con sus respectivas referencias para =60.

2.4.6 El controlador PID

Un controlador PID (Proporcional Integral Derivativo) es un sistema de control que

mediante un actuador, es capaz de mantener una variable o proceso en un punto deseado

dentro del rango de medicin del sensor que la mide. Es uno de los mtodos de control

ms frecuentes y precisos dentro de la regulacin automtica. Para el correcto

funcionamiento de un controlador PID que regule un proceso o sistema se necesita, al

menos:

Un sensor, que determine el estado del sistema por ejemplo un termmetro.

Un controlador, que genere la seal que gobierna al actuador.

Un actuador, que modifique al sistema de manera controlada (resistencia elctrica, motor, vlvula o bomba).

El sensor proporciona una seal analgica al controlador, la cual representa el

punto actual en el que se encuentra el proceso o sistema. La seal puede representar ese

valor en tensin elctrica, intensidad de corriente elctrica o frecuencia. En este ltimo

caso la seal es de corriente alterna, a diferencia de los dos anteriores, que son con

corriente continua. El controlador lee una seal externa que representa el valor que se

desea alcanzar. Esta seal recibe el nombre de punto de consigna (o punto de

referencia), la cual es de la misma naturaleza y tiene el mismo rango de valores que la

seal que proporciona el sensor. Para hacer posible esta compatibilidad, y que a su vez,

la seal pueda ser entendida por un humano, habr que establecer algn tipo de interfaz.

-

16

El controlador resta la seal de punto actual a la seal de punto de consigna,

obteniendo as la seal de error, que determina en cada instante la diferencia que hay

entre el valor deseado y el valor medido. La seal de error es utilizada por cada una de

las 3 componentes de un controlador PID propiamente dicho para generar las 3 seales

que sumadas componen la seal que el controlador va a utilizar para gobernar al

actuador. La seal resultante de la suma de estas tres seales, se llama variable

manipulada y no se aplica directamente sobre el actuador, si no que debe ser

transformada para ser compatible con el actuador que usemos.

Las tres componentes de un controlador PID son: parte proporcional, accin

integral y accin derivativa. El peso de la influencia que cada una de estas partes tiene en

la suma final, viene dado por la constante proporcional, el tiempo integral y el tiempo

derivativo, respectivamente. La parte proporcional consiste en el producto entre la seal

de error y la constante proporcional. Esta componente PID toma un papel importante

cuando la seal de error es grande, pero su accin se ve mermada con la disminucin de

dicha seal. Este efecto tiene como consecuencia la aparicin de un error permanente,

que hace que la parte proporcional nunca llegue a solucionar por completo el error del

sistema.

La constante proporcional determinar el error permanente, siendo ste menor

cuanto mayor sea el valor de la constante proporcional. Se pueden establecer valores

suficientemente altos en la constante proporcional como para que hagan que el error

permanente sea casi nulo pero, en la mayora de los casos, estos valores solo sern

ptimos en una determinada porcin del rango total de control, siendo distintos los

valores ptimos para cada porcin del rango. Sin embargo, existe tambin un valor lmite

en la constante proporcional a partir del cual, en algunos casos, el sistema alcanza

valores superiores a los deseados. Este fenmeno se llama sobre oscilacin y, por razones

de seguridad, no debe sobrepasar el 30%, aunque es conveniente que la parte

proporcional ni siquiera produzca sobre oscilacin. La parte proporcional no considera el

tiempo, por tanto la mejor manera de solucionar el error permanente y hacer que el

sistema contenga alguna componente que tenga en cuenta la variacin con respecto al

tiempo es incluyendo y configurando las acciones integral y derivativa.

El modo de control Integral tiene como propsito disminuir o eliminar el error en

estado estacionario, provocado por el modo proporcional. El error es integrado, lo cual

tiene la funcin de promediarlo o sumarlo por un periodo de tiempo determinado; Luego

es multiplicado por una constante I. I representa la constante de integracin.

-

17

Posteriormente, la respuesta integral es adicionada al modo Proporcional para formar el

control P + I con el propsito de obtener una respuesta estable del sistema sin error

estacionario. El modo integral presenta un desfasamiento en la respuesta de 90 que

sumados a los 180 de la retroalimentacin (negativa) acercan al proceso a tener un

retraso de 270, luego entonces solo ser necesario que el tiempo muerto contribuya con

90 de retardo para provocar la oscilacin del proceso. La ganancia total del lazo de

control debe ser menor a 1, y as inducir una atenuacin en la salida del controlador para

conducir el proceso a estabilidad del mismo.

La accin derivativa se manifiesta cuando hay un cambio en el valor absoluto del

error; (si el error es constante, solamente actan los modos proporcional e integral). El

error es la desviacin existente entre el punto de medida y el valor de consigna, o "La

consigna". La funcin de la accin derivativa es mantener el error al mnimo corrigindolo

proporcionalmente con la velocidad misma que se produce; de esta manera evita que el

error se incremente. Se deriva con respecto al tiempo y se multiplica por una constante D

y luego se suma a las seales anteriores (P+I). Gobernar la respuesta de control a los

cambios en el sistema ya que una mayor derivativa corresponde a un cambio ms rpido

y el controlador puede responder acordemente.

Significado de las constantes

P constante de proporcionalidad: se puede ajustar como el valor de la ganancia

del controlador o el porcentaje de banda proporcional.

I constante de integracin: indica la velocidad con la que se repite la accin

proporcional.

D constante de derivacin: hace presente la respuesta de la accin proporcional

(duplicndola), sin esperar (a que el error se duplique). El valor indicado por la constante

de derivacin es el lapso de tiempo durante el cual se manifestar la accin proporcional

correspondiente a 2 veces el error y despus desaparecer.

Tanto la accin Integral como la accin Derivativa, afectan a la ganancia dinmica

del proceso. La accin integral sirve para reducir el error estacionario, que existira

siempre si la constante Ki fuera nula.

-

18

Por tener una exactitud mayor a los controladores proporcional, proporcional

derivativo y proporcional integral el controlador PID se utiliza en aplicaciones ms

cruciales tales como control de presin, flujo, qumica, fuerza, velocidad y otras variables

adems de ser utilizado en reguladores de velocidad de automviles.

2.4.7 Reguladores de Tensin

Todos los circuitos electrnicos requieren de una o ms fuentes de alimentacin

estables de corriente continua para su funcionamiento, las fuentes DC convencionales

construidas con un transformador, un rectificador y un filtro (fuentes de alimentacin no

reguladas) no proporcionan una calidad suficiente ya que sus tensiones de salida varan

de acuerdo a la cantidad de corriente que circula por la carga y con la tensin de la lnea,

adems presentan una cantidad significativa de rizado a la frecuencia de la red. Por ello,

no son generalmente adecuadas para la mayora de las aplicaciones.

La funcin de un regulador de tensin es proporcionar una salida estable y bien

especificada, para alimentar a otros circuitos a partir de una fuente de alimentacin de

entrada de poca calidad; despus del amplificador operacional el regulador lineal es el

circuito integrado ms extensamente utilizado. Se pueden dividir a los reguladores de

tensin en dos grandes grupos, los reguladores conmutados y los lineales.

2.4.7.1 Reguladores Conmutados

Utilizan un transistor de potencia como un conmutador de alta frecuencia, de tal

manera de que la energa se transfiera de la entrada a la carga en forma de paquetes

discretos. Los pulsos de intensidad se transforman luego en corriente continua a travs

de un filtro inductivo y capacitivo. Puesto que, cuando el transistor opera como

conmutador consume menos potencia que cuando opera en su zona lineal, estos

reguladores son ms eficientes que los reguladores lineales; adems de ser ms

pequeos y ligeros.

Estos reguladores pueden disearse para que operen directamente con la tensin

de la red rectificada y filtrada sin necesidad del uso transformadores voluminosos; el

precio que se paga por esto es mayor complejidad del circuito y mayor ruido de rizado.

Los reguladores conmutados se utilizan mayormente en aplicaciones digitales en donde es

ms importante una alta eficiencia y un peso bajo que un poco de ruido de rizado a la

salida.

-

19

2.4.7.2 Reguladores Lineales

Controlan la tensin de salida ajustando continuamente la cada de tensin en un

transistor de potencia conectado en serie entre la entrada no regulada y la carga. Debido

a que el transistor conduce corriente continuamente, ste opera en su zona activa o

lineal. Aunque el regulador lineal es ms sencillo de utilizar que los reguladores

conmutados tienden a ser muy ineficientes debido a la potencia consumida por le

elemento de paso. La tendencia actual en el diseo de fuentes de alimentacin de varias

salidas en utilizar primero reguladores conmutados para aprovechar sus virtudes y luego

usar reguladores en serie o lineales para obtener tensiones de salidas ms limpias y

mejor reguladas.

Fig. 2.15: Diagrama de bloques de un regulador de tensin lineal

2.4.7.3 Regulador de Tensin en Serie

En la figura 2.16 se muestran 2 esquemas sencillos de reguladores de tensin en

serie, utilizando un transistor bipolar o un amplificador operacional como elemento de

control y un diodo zener como tensin de referencia y control del transistor u operacional.

El funcionamiento del circuito se basa en que si Vo disminuye, la tensin VBE del

transistor aumenta permitiendo as mayor paso de corriente y una restauracin en el

voltaje de salida. Ahora para el caso contrario donde el voltaje a la salida Vo aumenta, el

voltaje VBE del transistor disminuye, esto ocasiona que la corriente de salida disminuya

intentando as disminuir el voltaje de salida hasta restaurarlo al valor deseado.

-

20

Fig. 2.16: a) Regulador de tensin en serie simple. b) Regulador de tensin en serie

basado en un AO

Ahora una versin mejorada de ste regulador de tensin lineal se implementa

utilizando un amplificador operacional, un par Darlington (Q1 y Q2) y una referencia de

tensin. Esta configuracin con par darlington brinda una ganancia de corriente alta,

generalmente de 1000 o ms. En el circuito 2.16.b el AO acta como amplificador de

error entre el voltaje de referencia VREF y el voltaje obtenido a travs de la red de

realimentacin formada por R1 y R2.

2.4.8 Comunicacin y Transmisin de Datos

En cualquier proceso o sistema, bien sea mecnico, elctrico, qumico, etc. Es

necesaria la comunicacin entre subsistemas o subprocesos y la supervisin del mismo

por parte de un operario, estos da pie a desarrollar algoritmos o esquemas de

comunicacin que faciliten dichas tareas. A continuacin se describirn muy brevemente

el bus de comunicacin I2C y el protocolo de comunicacin serial, ambos ampliamente

utilizados en este proyecto.

2.4.8.1 Bus I2C

I2C es un bus de comunicaciones serie. Su nombre viene de Inter-Integrated

Circuit (Circuitos Inter-Integrados). La versin 1.0 data del ao 1992 y la versin 2.1 del

ao 2000, su diseador es la empresa Philips. La velocidad es de 100Kbits por segundo

en el modo estndar, aunque tambin permite velocidades de 3.4 Mbit/s. Es un bus muy

usado en la industria, principalmente para comunicar microcontroladores y sus perifricos

-

21

en sistemas empotrados (Embedded Systems) y generalizando ms para comunicar

circuitos integrados entre si que normalmente residen en un mismo circuito impreso.

Fig. 2.17: Estructura de un BUS I2C

La principal caracterstica de I2C es que utiliza dos lneas para transmitir la

informacin: una para los datos y por otra la seal de reloj. Tambin es necesaria una

tercera lnea, pero esta slo es la referencia (masa). Como suelen comunicarse circuitos

en una misma placa que comparten una misma masa, esta tercera lnea no suele ser

necesaria. Las dos primeras lneas son drenador abierto, por lo que necesitan resistencias

de pull-up.

Las lneas se llaman:

SDA (Sistema de data): lnea por la cul viajan los datos entre dispositivos.

SCL (Sistema de reloj): lnea por la cul transita la seal de reloj del sistema.

GND (Tierra): masa.

Los dispositivos conectados al bus I2C tienen una direccin nica para cada uno.

Tambin pueden ser maestros o esclavos. El dispositivo maestro inicia la transferencia de

datos y adems genera la seal de reloj, pero no es necesario que el maestro sea

siempre el mismo dispositivo, esta caracterstica se la pueden ir pasando los dispositivos

que tengan esa capacidad. Esta caracterstica hace que al bus I2C se le denomine bus

multimaestro.

Las transacciones en el bus I2C tienen este formato:

| Inicio | A7 A6 A5 A4 A3 A2 A1 | L/E | REC | ... DATOS ... | parada | espera |

-

22

El bus esta libre cuando SDA y SCL estn en estado lgico alto.

En estado bus libre, cualquier dispositivo puede ocupar el bus I2C como maestro.

El maestro comienza la comunicacin enviando un patrn llamado "condicin de inicio". Esto alerta a los dispositivos esclavos, ponindolos a la espera de una

transaccin.

El maestro se dirige al dispositivo con el que quiere hablar, enviando un byte que contiene los siete bits (A7-A1) que componen la direccin del dispositivo esclavo

con el que se quiere comunicar, y el octavo bit (A0) de menor peso se corresponde

con la operacin deseada (L/E), lectura=1 (recibir del esclavo) y escritura=0

(enviar al esclavo).

La direccin enviada es comparada por cada esclavo del bus con su propia direccin, si ambas coinciden, el esclavo se considera direccionado como esclavo-

transmisor o esclavo-receptor dependiendo del bit L/E.

El esclavo responde enviando un bit de REC que le indica al dispositivo maestro que el esclavo reconoce la solicitud y est en condiciones de comunicarse.

Seguidamente comienza el intercambio de informacin entre los dispositivos.

El maestro enva la direccin del registro interno del dispositivo que se desea leer o escribir.

El esclavo responde con otro bit de REC

Ahora el maestro puede empezar a leer o escribir bytes de datos. Todos los bytes de datos deben constar de 8 bits, el nmero mximo de bytes que pueden ser

enviados en una transmisin no est restringido, siendo el esclavo quien fija esta

cantidad de acuerdo a sus caractersticas.

Cada byte ledo/escrito por el maestro debe ser obligatoriamente reconocido por un bit de REC por el dispositivo maestro/esclavo.

Se repiten los 2 pasos anteriores hasta finalizar la comunicacin entre maestro y esclavo.

-

23

Aun cuando el maestro siempre controla el estado de la lnea del reloj, un esclavo de baja velocidad o que deba detener la transferencia de datos mientras efecta

otra funcin, puede forzar la lnea SCL a nivel bajo. Esto hace que el maestro entre

en un estado de espera, durante el cual, no transmite informacin esperando a

que el esclavo est listo para continuar la transferencia en el punto donde haba

sido detenida.

Cuando la comunicacin finaliza, el maestro transmite una "condicin de parada" para dejar libre el bus.

Despus de la "condicin de parada", es obligatorio para el bus estar en espera durante unos microsegundos.

2.4.8.2 Protocolo Serial

La comunicacin serial es un protocolo muy comn (no hay que confundirlo con el

Bus Serial de Comunicacin, o USB) para comunicacin entre dispositivos y que se incluy

hasta hace poco de manera estndar en prcticamente cualquier computadora, siendo

progresivamente abandonado a favor de la interfaz USB. La mayora de las computadoras

que poseen este sistema de comunicacin incluyen dos puertos seriales RS-232. La

comunicacin serial es tambin un protocolo comn utilizado por varios dispositivos para

instrumentacin; existen varios dispositivos compatibles con GPIB (General purpose

instrumental bus) que incluyen un puerto RS-232. Adems, la comunicacin serial puede

ser utilizada para adquisicin de datos si se usa en conjunto con un dispositivo remoto de

muestreo.

El concepto de comunicacin serial es sencillo. El puerto serial enva y recibe bytes

de informacin un bit a la vez. Aun y cuando esto es ms lento que la comunicacin en

paralelo, que permite la transmisin de un byte completo por vez, este mtodo de

comunicacin es ms sencillo y puede alcanzar mayores distancias. Por ejemplo, la

especificacin IEEE 488 para la comunicacin en paralelo determina que el largo del cable

para el equipo no puede ser mayor a 20 metros, con no ms de 2 metros entre

cualesquier dos dispositivos; por el otro lado, utilizando comunicacin serial el largo del

cable puede llegar a los 1200 metros.

Tpicamente, la comunicacin serial se utiliza para transmitir datos en formato

ASCII. Para realizar la comunicacin se utilizan 3 lneas de transmisin: (1) Tierra (o

referencia), (2) Transmitir, (3) Recibir. Debido a que la transmisin es asincrnica, es

-

24

posible enviar datos por una lnea mientras se reciben datos por otra. Existen otras lneas

disponibles para realizar handshaking, o intercambio de pulsos de sincronizacin, pero no

son requeridas. Las caractersticas ms importantes de la comunicacin serial son la

velocidad de transmisin, los bits de datos, los bits de parada, y la paridad. Para que dos

puertos se puedan comunicar, es necesario que las caractersticas sean iguales.

Velocidad de transmisin (baud rate): Indica el nmero de bits por segundo que se transfieren, y se mide en baudios (bauds). Por ejemplo, 300 baudios

representa 300 bits por segundo. Cuando se hace referencia a los ciclos de

reloj se est hablando de la velocidad de transmisin. Por ejemplo, si el

protocolo hace una llamada a 4800 ciclos de reloj, entonces el reloj est

corriendo a 4800 Hz, lo que significa que el puerto serial est muestreando

las lneas de transmisin a 4800 Hz. Las velocidades de transmisin ms

comunes para las lneas telefnicas son de 14400, 28800, y 33600. Es

posible tener velocidades ms altas, pero se reducira la distancia mxima

posible entre los dispositivos. Las altas velocidades se utilizan cuando los

dispositivos se encuentran uno junto al otro, como es el caso de

dispositivos GPIB.

Bits de datos: Se refiere a la cantidad de bits en la transmisin. Cuando la computadora enva un paquete de informacin, el tamao de ese paquete

no necesariamente ser de 8 bits. Las cantidades ms comunes de bits por

paquete son 5, 7 y 8 bits. El nmero de bits que se enva depende en el

tipo de informacin que se transfiere. Por ejemplo, el ASCII estndar tiene

un rango de 0 a 127, es decir, utiliza 7 bits; para ASCII extendido es de 0 a

255, lo que utiliza 8 bits. Si el tipo de datos que se est transfiriendo es

texto simple (ASCII estndar), entonces es suficiente con utilizar 7 bits por

paquete para la comunicacin. Un paquete se refiere a una transferencia de

byte, incluyendo los bits de inicio/parada, bits de datos, y paridad. Debido a

que el nmero actual de bits depende en el protocolo que se seleccione, el

trmino paquete se usar para referirse a todos los casos.

Bits de parada: Usado para indicar el fin de la comunicacin de un solo paquete. Los valores tpicos son 1, 1.5 o 2 bits. Debido a la manera como

se transfiere la informacin a travs de las lneas de comunicacin y que

cada dispositivo tiene su propio reloj, es posible que los dos dispositivos no

estn sincronizados. Por lo tanto, los bits de parada no slo indican el fin de

-

25

la transmisin sino adems dan un margen de tolerancia para esa

diferencia de los relojes. Mientras ms bits de parada se usen, mayor ser

la tolerancia a la sincrona de los relojes, sin embargo la transmisin ser

ms lenta.

Paridad: Es una forma sencilla de verificar si hay errores en la transmisin serial. Existen cuatro tipos de paridad: par, impar, marcada y espaciada. La

opcin de no usar paridad alguna tambin est disponible. Para paridad par

e impar, el puerto serial fijar el bit de paridad (el ltimo bit despus de los

bits de datos) a un valor para asegurarse que la transmisin tenga un

nmero par o impar de bits en estado alto lgico. Por ejemplo, si la

informacin a transmitir es 011 y la paridad es par, el bit de paridad sera 0

para mantener el nmero de bits en estado alto lgico como par. Si la

paridad seleccionada fuera impar, entonces el bit de paridad sera 1, para

tener 3 bits en estado alto lgico. La paridad marcada y espaciada en

realidad no verifican el estado de los bits de datos; simplemente fija el bit

de paridad en estado lgico alto para la marcada, y en estado lgico bajo

para la espaciada. Esto permite al dispositivo receptor conocer de

antemano el estado de un bit, lo que servira para determinar si hay ruido

que est afectando de manera negativa la transmisin de los datos, o si los

relojes de los dispositivos no estn sincronizados.

-

26

3. Sistema Adjudicado

3.1. Presentacin

Este proyecto tiene como objetivo principal disear, elaborar e implementar un

rectificador trifsico controlado mediante un control discreto (PID digital), pero este

rectificador estar embebido en una fuente DC de laboratorio, la cul esta

preliminarmente diseada y construida. No es objetivo de dicho proyecto describir a

fondo la metodologa de diseo, ni los argumentos por los cuales se adoptaron ciertas

topologas en la implementacin de la antes mencionada fuente DC; porque simplemente

es el sistema entregado.

3.2. Esquema de la Fuente DC

A continuacin se describir a detalle todo el sistema preliminar adjudicado por el

profesor Julio Walter. Inicialmente se expondr un esquema bsico de la fuente, el cual se

muestra en la figura 3.1.

Fig. 3.1: Esquema bsico de la fuente con control independiente entre el rectificador y el

regulador.

-

27

La fuente DC esta fundamentada en el esquema de una fuente regulada

ampliamente conocido, slo que el elemento regulador en ste caso es un transistor de

potencia (IGBT) regido bajo un sistema de regulacin lineal, dicha fuente consta de un

transformador trifsico de potencia, seguido de un rectificador trifsico completamente

controlado, luego un filtro LC y por ltimo el elemento regulador tambin completamente

controlado con un pequeo condensador que sirva de filtro para evitar el rizado a la

salida.

3.2.1 El Transformador de Potencia

El transformador usado es un transformador trifsico de potencia, de 20kVA, con

configuracin delta en su devanado primario y voltaje 208Vrms fase-fase; y en el

devanado secundario de configuracin estrella y voltaje 132Vrms fase-neutro

aproximadamente. El voltaje en el secundario del transformador es aproximado debido a

que el fabricante del mismo, construy dos transformadores de configuracin

delta/estrella de 10kVA cada uno y luego los conecto en paralelo como se muestra en la

figura 3.2, quizs por razones de infraestructura. Gracias a esto existe un desbalance

entre los devanados del transformador que genera variaciones en los voltajes fase-neutro

de cada fase en particular

Fig. 3.2: Configuracin del transformador de potencia

-

28

En la figura 3.3 se puede observar el detalle del transformador de potencia

debidamente instalado en el chasis, vale la pena destacar que el chasis tambin es parte

del sistema adjudicado; tambin puede verse lo robusto del transformador trifsico con

un peso aproximado de 100kgr, tpico en fuentes de poder con regulacin lineal donde los

transformadores son grandes y pesados.

Fig. 3.3: Detalle del transformador y parte del chasis

3.2.2 Modulo Rectificador y Filtro LC

Para la etapa de rectificacin fue entregado un juego de 6 tiristores encapsulados

en pares, tpicamente utilizados en rectificacin trifsica, estos tiristores estn ya

instalados sobre un disipador especficamente diseado para ellos y su respectivo

extractor o ventilador, todos estos dispositivos provenientes de la casa SEMIKRON. El

cdigo de los tiristores es SKKT91/04 capaz de circular 150A a travs de ellos en

operacin continua y excelentes caractersticas en conmutacin. En la figura 3.4 se

observa el encapsulado con 2 tiristores y la simbologa respectiva, adems se puede

observar lo fcil de las conexiones y lo cmodo de su montaje.

Toda esta etapa de rectificacin y filtrado conforma un esquema como el mostrado

en la figura 3.5 donde se puede observar los 6 tiristores dispuestos en pares, en forma de

-

29

3 ramas las cuales se encargan de rectificar completamente la red trifsica con el control

apropiado de los tiristores; dicho sistema de control se describir en captulos posteriores.

El filtro LC (inductor y condensador) esta compuesto por una bobina de 1.4mH y 150Amp

fabricada por la casa Transmagneca, la figura 3.6 muestra la bobina de aproximadamente

50kgr. El condensador de 9600uf esta compuesto por 4 condensadores de 2400uf y 450v

de la casa Mallory conectados en paralelo.

Fig. 3.4: Empaque del SKKT91/04 y su respectivo smbolo

Fig. 3.5: Circuito rectificador y filtro LC

Para disponer de un montaje fcil y sencillo del filtro y el rectificador, fue tambin

entregado como parte del chasis un modulo metlico donde reposarn los condensadores

y el disipador con el puente rectificador trifsico, adems en este mdulo tambin irn

instalados el condensador de salida y el elemento regulador. El detalle de ste modulo

puede verse en la figura 3.7.

-

30

Fig. 3.6: Bobina del filtro LC 1,4mH @ 150Amp

Fig. 3.7 Detalle del mdulo metlico, los tiristores y el banco de condensadores

3.2.3 Tarjetas de Control, Visualizadora y Fuente Conmutada

Con el fin de controlar todo el funcionamiento y monitorear el desempeo de la

fuente, la misma viene con un par de circuitos impresos que pueden definirse como la

tarjeta de control y la tarjeta visualizadora, estos dos circuitos impresos se comunican

entre si mediante un bus serial, utilizando un protocolo similar al I2C ambos circuitos

-

31

impresos estn alimentados por una fuente DC conmutada altamente comercial de la casa

AUTEC de salida +5 y +12. En la figura 3.8 se puede ver el detalle de las tarjetas.

Fig. 3.8: Tarjetas de Control, Visualizadora y Fuente Conmutada, entregadas.

3.2.3.1 Tarjeta de Control

La tarjeta de control entregada es una tarjeta bastante compleja la cul esta

constituida bsicamente por un FPGA (Field Programmable Gate Array) que es un

dispositivo semiconductor que contiene bloques de lgica cuya interconexin y

funcionalidad se puede programar, un PIC (Peripheral Interface Contoller) que es un

microcontrolador y varios perifricos. El PIC y FPGA trabajan en una configuracin

maestro-esclavo respectivamente, gestionando el funcionamiento de toda la tarjeta y sus

perifricos, este funcionamiento se describir con ms detalle en captulos posteriores.

Los perifricos que posee la tarjeta se detallan a continuacin: