Tarea_1_0939304

-

Upload

sebastian-parra-quiroga -

Category

Documents

-

view

48 -

download

0

Transcript of Tarea_1_0939304

-

1

Resumen A travs de este documento se presenta el desarrollo en cdigo VHDL de un sumador de acarreo en

adelanto de 16 bits concebido a partir de grupos de sumadores de

acarreo en adelanto de 4 bits. Se presenta tambin resultados de

simulacin realizada en el software Quartus II v9.1 Web Edition

as como un anlisis de tiempo, consumo de potencia y recursos

considerando su implementacin en una FPGA de la familia

Stratix II.

Conceptos Clave Sumador de acarreo en adelanto, Sumador

de acarreo propagado.

I. INTRODUCCIN

Un sumador completo es un circuito electrnico que suma dos

nmeros binarios teniendo en consideracin un valor de carry

en la entrada del circuito. Como salidas este circuito

proporciona el valor de la suma y un carry de salida. La figura

1 ilustra un sumador completo de un bit donde es posible

identificar los sumandos A y B, el carry de entrada Ci como

las entradas del circuito y la suma S y el carry de salida Co

como las salidas del circuito. Para generar un circuito capaz de

sumar nmeros de ms bits basta con poner en cascada n

sumadores completos como el de la figura 1, donde n

corresponde al nmero de bits de los sumandos; es preciso

acotar que la conexin en casada hace referencia a que el carry

de salida de un sumador completo debe conectarse al carry de

entrada del sumador siguiente, as el sumador completo de n

bits solo tendr un carry de entrada y un carry de salida. La

figura 2 ilustra un diagrama de bloques de un sumador

completo de 16 bits donde cada bloque de color verde

corresponde a un sumador completo de 1 bit.

Fig. 1. Diagrama resultante del RTL Viewer de un sumador completo de 1 bit

implementado en VHDL mediante el software Quartus II v9.1 Web Edition.

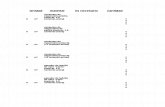

Utilizando la herramienta Vector Waveform de Quartus II

v9.1 Web Edtion, se simularon tres operaciones para el

circuito de la figura 2, los resultados se ilustran en la figura 3.

Fig. 3. Vector Waveform resultante de la simulacin de tres operaciones

realizadas en el sumador completo de 16 bits de la figura 2.

En la figura 3 es posible evidenciar un retardo en la

simulacin cada vez que se presenta un cambio en el valor de

los sumandos y/o de carry de entrada. Este retardo est

siempre presente en los circuitos electrnicos y es

imprescindible minimizarlo tanto como sea posible para una

mayor eficiencia en la implementacin del circuito. Para el

circuito de la figura 2, se ha realizado un anlisis de ruta

crtica gracias a la herramienta Timing Analyzer de Quartus II

v9.31 Web Edition y el resultado arroja un valor de 15.149 ns

para la ruta desde el bit 1 del sumando A hasta el bit 14 de la

suma S. Un sumador completo de n bits de conexin en

cascada o Ripple Carry Adder no tiene un desempeo eficiente

debido a la propagacin del carry de entrada a travs de todos

y cada uno de los sumadores completos que conformen el

circuito. Considerando esto se desarrollaron los sumadores de

acarreo en adelanto o Carry Look Ahead Adder. Mediante este

documento se presenta el desarrollo en cdigo VHDL de un

sumador de acarreo en adelanto de 16 bits concebido a partir

de grupos de sumadores de acarreo en adelanto de 4 bits. Se

presenta tambin resultados de simulacin realizada en el

software Quartus II v9.1 Web Edition asi como un anlisis de

ruta crtica, consumo de potencia y recursos considerando su

implementacin en una FPGA de la familia Stratix II.

16 Bit Carry-Look-Ahead Adder basado en

4 Bit Carry-Look-Ahead Adder

Parra Q. Jhoan Sebastian,

Escuela de Ingeniera Elctrica y Electrnica - Facultad de Ingeniera,

Universidad del Valle

-

2

Fig. 2. Diagrama RTL Viewer de un sumador completo de acarreo propagado de 16 bits implementado en VHDL mediante el software Quartus II v9.1 Web

Edition.

II. SUMADOR DE ACARREO EN ADELANTO DE 4 BITS.

La figura 4 ilustra el diagrama RTL Viewer de un sumador de

acarreo en adelanto de 4 bits desarrollado en cdigo VHDL.

Fig. 4. Diagrama RTL Viewer de un sumador completo de acarreo en adelanto 4 bits implementado en VHDL mediante el software Quartus II v9.1 Web Edition

Un sumador de acarreo en adelanto o carry look ahead adder

mejora la velocidad de clculo mediante la reduccin de la

cantidad de tiempo requerido para determinar los bits de carry.

En el sumador de acarreo propagado, ms simple pero ms

lento, la propagacin del carry de entrada se da porque este se

calcula junto con el bit de suma, y cada sumador debe esperar

hasta que el carry anterior se haya calculado para empezar a

calcular su propio resultado. El sumador acarreo en adelanto

calcula uno o ms bits de carry antes de la suma, lo que reduce

el tiempo de espera para calcular el resultado de los bits de

valor ms grandes.

Es recomendable la implementacin de bloques de sumadores

de acarreo en adelanto con un mximo de 4 bits, y si se hace

necesario, conectar estos bloques en cascada para obtener

sumas ms grandes ya que la lgica combinacional requerida

tiene un crecimiento exponencial con el nmero de bits de los

sumandos lo que podra ocasionar que se pierda la eficiencia

alcanzada con el acarreo en adelanto.

P = A B; G = AB;

S0 = Ci P0; S1 = C0 P1; S2 = C1 P2; S3 = C2 P3;

C0 = P0Ci + G0;

C1 = P1G0 + CiP0P1 + G1; C2 = G2 + P2G1 + G0P1P2 + CiP0P1P2;

CO = G3 + P3G2 + G1P2P3 + G0P1P2P3 + CiP0P1P2P3;

Go = G3 + G2P3 + G1P2P3 + G0P1P2P3; Po = P0P1P2P3;

-

3

Las ecuaciones booleanas anteriormente mostradas

representan los clculos lgicos que genera el circuito de la

figura 4. Las seales Po y Go se tienen como salida para la

futura implementacin del circuito como parte de un sumador

de 16 bits. De estas ecuaciones se puede evidenciar que el

carry de cada bit se descompone en dos, un carry generado y

carry propagado. P y G no dependen de ningn carry, por lo

que la sumatoria no tiene est sujeta a ningn valor de carry

anterior y el acarreo de cada bit es calculable de manera

independiente.

III. SUMADOR DE ACARREO EN ADELANTO DE 16 BITS.

Considerando bloques de 4 bits, se implementa un sumador de

acarreo en adelanto de 16 bits cuyo diagrama RTL Viewer se

presenta en la figura 5.

Fig. 5. Diagrama RTL Viewer de un sumador completo de acarreo en adelanto de 16 bits implementado en VHDL mediante el software Quartus II v9.1 Web

Edition.

La implementacin del sumador de acarreo en adelanto de 16

bits utiliz cuatro bloques sumadores de acarreo en adelanto

de 4 bits y un bloque extra capaz de calcular los acarreos de

manera independiente, el bloque CLAG.

La figura 6 ilustra el Vector Waveform resultante de simular

en el CLA Adder de 16 bits, las mismas operaciones que

muestra la figura 3. Un anlisis de tiempo mediante la

herramienta Timing Analyzer del software Quartus II arroj

como resultado un tiempo de 13.861 ns para una ruta que va

desde el bit 3 de B hasta el bit 11 de S, como peor caso. Es

evidente con este resultado como hay una mejora en los

retardos del sumador implementado.

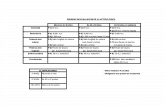

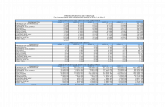

Las figuras 7 y 8 muestran el reporte de consumo de recursos

para el sumador de acarreo propagado de 16 bits y el sumador

de acarreo en adelanto de 16 bits, respectivamente.

Fig. 6. Vector Waveform resultante de la simulacin de tres operaciones

realizadas en el sumador completo de 16 bits de la figura 5.

-

4

Fig. 7. Diagrama RTL Viewer de un sumador completo de acarreo propagado de 16 bits implementado en VHDL mediante el software Quartus II v9.1 Web

Edition.

Fig. 8. Reporte de compilacin y anlisis de potencia de un sumador completo de acarreo en adelanto de 16 bits implementado en VHDL mediante el software

Quartus II v9.1 Web Edition.