LAB4_Contador_Asincrono

-

Upload

rodney-rodas-regalado -

Category

Documents

-

view

70 -

download

2

Transcript of LAB4_Contador_Asincrono

UNIVERSIDAD NACIONAL DE INGENIERIA

FACULTAD DE INGENIERIA MECANICA

LABORATORIO Nº 4

CONTADOR ASINCRONO

OBJETIVOImplementar un contador binario de 4 bits con 4 flip-flops tipo JK maestro-esclavo.

MATERIAL Y EQUIPO1 Circuito integrado 74734 Resistencia de 220Ω4 Diodo ledFuente de Alimentación Generador de funcionesOsciloscopio INFORME PREVIO

1. Efectuar la tabla de la verdad de un flip-flop tipo JK y de un flip-flop tipo T.

a) TIPO JK b) TIPO “T”

2. ¿Cómo se convierte un FF tipo JK en uno tipo T?

3. Estudiar el funcionamiento del integrado 7473 que contiene dos flip-flop independientes tipo JK maestro-esclavo con opción de "clear".

4. ¿Cuantos flip-flop hay en un chip 7473?

5. ¿Cual es el pin de Vcc?

6. ¿Cual es el pin de tierra?

7. ¿Cuales son los pines de CLEAR?

8. ¿Cuales los de las salidas Q?

9. ¿Cuales de las entradas J?

10. ¿Cuales de las entradas K?

11. ¿Como se resetean a cero los FF, con un 1 o con un 0 en la entrada de CLEAR?

J K Qn+1

12. Se va a diseñar un circuito contador binario tipo "ripple" de 4 bits. Para ello se necesitan 4 flips-flops tipo T que pueden obtenerse de 4 flip-flops tipo JK (dos integrados 7473). La forma de conectar los flip-flops se muestra en la figura.(Los números corresponden a los pines de cada chip)

13. Completar el siguiente diagrama de tiempo en el que aparecen las señales Clock, Q0, Q1, Q2, Q3 y visualizar el valor de la cuenta.

14. ¿Cual es el bit menos significativo?

15. ¿Cuando encienden los leds, cuando Q = 0 o cuando Q = 1?

16. Si en lugar de utilizar la salida Q para encender los leds, se utiliza la salida Q, indique la forma de conexión mostrando claramente la polaridad del led. dibuje el led en la forma como lo conectaría

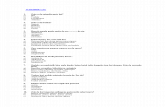

PROCEDIMIENTO

S 1C L O C K 1

R 3

2 2 0

D 1

L E D

U 1 B

7 4 L S 7 3 A

7

5

1 0

6

9

8

411

J

C L K

K

CLR

Q

Q

VC

CG

ND

U 2 A

7 4 L S 7 3 A

1 4

1

32

1 2

1 34

11

J

C L K

KC

LR

Q

QV

CC

GN

D

V 15 V d c

D 2

L E D

U 2 B

7 4 L S 7 3 A

7

5

1 0

6

9

8

411

J

C L K

K

CLR

Q

Q

VC

CG

ND

R 2

2 2 0

0

D 3

L E DR 4

2 2 0

R 1

2 2 0

D 4

L E D

U 1 A

7 4 L S 7 3 A

1 4

1

3

2

1 2

1 3

411

J

C L K

K

CLR

Q

Q

VC

CG

ND

1. Armar el circuito del contador asíncrono

2. Identificar los led con la salida Q correspondiente (Q0, Q1, Q2, Q3).

3. Alimentar la señal CLOCK del primer flip-flop.

4. Colocar el switch de las señales de CLEAR para que todos los flip flops se inicialicen en cero. (los leds conectados a dichas salidas estarán apagados)

5. Ajustar el CLOCK para mínima frecuencia (1 Hz). Colocar el switch de las señales de CLEAR en la posición para contar. Poco a poco el contador debe comenzar a contar, lo cual se apreciará en la secuencia de Encendido de los LEDS que corresponderá a un conteo binario de 4 bits; desde 0000 hasta 1111. Si se aumenta la frecuencia del generador de señales el conteo será más veloz.

6. Diseñe e implemente un contador asíncrono ascendente que cuente del 0 al 13. Recuerde que es una cuenta truncada.

7. Dibuje el circuito, con todas las compuertas necesarias, indicando tipo de chips y número de los pines. Arme el circuito y compruebe su funcionamiento.

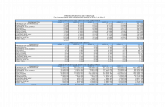

INFORME FINAL1. Presentar el diagrama lógico de cada circuito y su diagrama de tiempo correspondiente.

2. Observaciones y Conclusiones