Guias_y_Practicas_2041_8

-

Upload

jonathan-hernan-benites-saenz -

Category

Documents

-

view

217 -

download

0

description

Transcript of Guias_y_Practicas_2041_8

TERCER PARCIAL

GUA DE PRACTICA No. 3.2

Tema:Anlisis de Mquinas secuenciales sincrnicas

1. Objetivo.Dibujar el diagrama de estados de una mquina secuencial sincrnica y verificar su funcionamiento mediante la implementacin del circuito electrnico correspondiente.

2. Materiales y Equipos. Materiales. Protoboard Elementos biestables, compuertas lgicas, circuitos MSI. Resistencias Pulsador mecnico Diodos led Displays Cables

Equipos: Fuente de alimentacin Computador Multmetro Digital

3. Procedimiento

3.1 Implementar el circuito planteado

3.2 Conecte la fuente de alimentacin ( 5V DC) a su circuito y compruebe el funcionamiento del mismo verificando que el diseo cumpla con el diagrama de estados obtenido en su trabajo preparatorio. Recuerde verificar todas las combinaciones posibles de sus entradas para cada estado.

3.3 Apague la fuente de alimentacin y encindala luego de unos pocos segundos y verifique el funcionamiento de su circuito inicializador.

3.4 Realice el reseteo de su mquina secuencial sincrnica en cualquier instante del diagrama de estados y verifique el funcionamiento combinado tanto de su circuito inicializador como de su circuito antirebotes.

En caso de mal funcionamiento realice los pasos 3.5 y 3.6

3.5 NO desarme el circuito implementado. Como primer paso verifique conexiones, continuidad, voltaje de la fuente de alimentacin, alimentacin de los integrados, voltaje de las entradas asincrnicas, seal de reloj, etc.

3.6 Si la falla se mantiene prosiga a medir y verificar voltajes en el circuito (0L= aprox. 0V, 1L=aprox. 5V). Se recomienda realizar las mediciones desde la salida del circuito hacia las entradas, haciendo uso del multmetro digital. Tome en cuenta que para circuitos secuenciales las mediciones debe hacerlas usando una seal de reloj manual, caso contrario no podr verificar resultados.

Realice las mediciones por bloques (DP, EM, DS)

NRC 2041

Diseo 3.2

Tema:Anlisis de Mquinas secuenciales sincrnicas

1. Objetivo:

Dibujar el diagrama de estados de una mquina secuencial sincrnica y verificar su funcionamiento mediante la implementacin del circuito electrnico correspondiente.

2. Circuito a implementar:

3. Diagrama de bloques correspondiente

4. Anlisis paso a paso del circuito dado

Dada una red secuencial sincrnica se desea obtener su diagrama de estados. Y a partir de ste, inferir el funcionamiento de la mquina. En el esquema general, se ilustran los elementos de memoria como flip-flops D.

Figura 1. Esquema mquina secuencial empleando flip-flops D

El estado actual es sostenido en las salidas Q de los flip-flops, durante el intervalo t. En este intervalo, se generan D0, D1, D2. Estas ltimas se llevan a las entradas de los flip-flops. De tal manera que en el instante (t) las salidas de los flip-flops, que memorizan el estado, dependen del decodificador de prximo estado. Para esto es indispensable que las entradas a los flip-flops sean estables en el momento de aplicar la seal del reloj que efectuar la conmutacin, o cambio de estado (pasar del intervalo t-1 al intervalo t).

Paso 1.

Para realizar el anlisis de nuestra maquina secuencial lo primero que debemos hacer es realizar el diagrama de nuestra maquina secuencial como se muestra en la figura 1.

Paso 2.

Redibujamos y realizamos el anlisis en lgica mixta tanto de las entras como de las salidas para hallar la funciones del D.P y del D.S que nos ayudaran a realizar la tabla de estados.

DECODIFICADOR DE PRXIMO ESTADO Figura 2. Esquema de entradas empleando compuertas lgicas

Figura 3. Esquema de entradas empleando compuertas Duales

FUNCIONES DEL DECODIFICADOR DE PRXIMO ESTADO

DECODIFICADOR DE SALIDA Figura 4. Esquema de entradas empleando compuertas lgicas

Figura 5. Esquema de entradas empleando compuertas Duales

FUNCIONES DEL DECODIFICADOR DE SALIDA

Paso 3.Antes de realizar la tabla de estados debemos realizar el respectivo mapa k (mapas de karnaugh) para cada funcin.

MAPAS K PARA DECODIFICADOR DE PRXIMO ESTADO

MAPAS K PARA DECODIFICADOR DE SALIDA

PASO 4.

Por ultimo realizamos la tabla de prximo estado de nuestra maquina secuencial.

XD0D1D2Q2Q1Q0Z1Z2

000010000100

000110110100

001010000100

001110000100

010010110100

010111111100

011000110000

011111111100

100010000100

100101001001

101010000100

101101111000

110010000100

110111111110

111000000000

111111111100

PASO 5.

Realizamos nuestro respectivo diagrama de estados siguiendo la tabla de estados que hicimos anteriormente.

DIAGRAMA DE ESTADOS

5. Dibujar el diagrama de tiempos y diagrama de estados correspondiente.

DIAGRAMA DE TIEMPOS

PARA D0

PARA D1

PARA D2

DIAGRAMA DE ESTADOS

6. Implementar la maquina secuencial y verificar el cumplimiento del diagrama de estados obtenido.

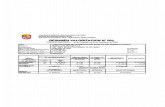

7. Lista de elementos

3 Capacitores

CantidadReferenciaValorCdigo

2C1,C310u

1C210uMaplin KQ69A

5 Resistencias

CantidadReferenciaValor

2R1,R4220R

1R2330R

1R3150k

1R61k

10 Circuitos Integrados

CantidadReferenciaValor

2U1-U274HCT74U1(1/1)-U2(1/1)

1U374HC21U3(2/2)

1U47404U4(1/6)

1U57420U5(2/2)

1U67410U6(2/3)

3U7,U9-U107400U7(4/4)-U9(4/4)-U10(1/4)

1U8555U8(1/1)

3 Diodos

CantidadReferenciaValorCdigo

1D2LED-BIBY

2D3-D4DIODE1N4001

2 Otros

CantidadReferenciaValorCdigo

1DSW1DIPSW_2Dip switch

1RV1100kPotencimetro

8. Conclusiones y recomendaciones

CONCLUSIONES Los circuitos combinacionales producen salidas inmediatamente despus de que sus entradas cambian. Los circuitos secuenciales requieren de la seal de reloj para producir cambios en las salidas.

Los circuitos secuenciales bsicos son los flip flops.

El comportamiento de los circuitos secuenciales puede ser expresado utilizando tablas de estado y diagramas de estado.

RECOMENDACIONES

El nmero de los terminales de los integrados que se corresponden con las entradas del elemento que se est utilizando.

Elegir para cada conexin el cable ms adecuado: aquel que no sea mucho ms largo de lo que se necesita. - Marcar las conexiones sobre el esquema como ya realizadas a medida que se vayan realizando. De este modo no se olvidar ninguna.

Antes de conectar la alimentacin del circuito, comprobar que los integrados tienen correctamente conectados los terminales de alimentacin y que el circuito se encuentra correctamente montado.

Probar el circuito comenzando por las partes funcionales pequeas e ir aadiendo nuevos bloques una vez que se haya comprobado el funcionamiento del bloque anterior. Esto facilitar la deteccin y solucin de posibles errores de montaje.

9. Bibliografa

TTL Logic, Standard TTL, Schottky, Low Power Schottky, Texas Instruments Inc., 1988inal del formulario