E5_PLAs13_2

-

Upload

jean-carlo-canevello -

Category

Documents

-

view

7 -

download

1

Transcript of E5_PLAs13_2

UNIVERSIDAD NACIONALMAYOR DE SAN MARCOS

Decana de AméricaFACULTAD DE INGENIERÍA DE SISTEMAS E INFORMATICA

SISTEMAS DIGITALESMg. JUAN CARLOS GONZALES SUAREZ

2013-II

Sistemas DigitalesMg. Juan Carlos Gonzales Suárez

Funciones Lógicas

F = Suma de Productos = Σ ( minterm)

X Y

P1

P2

P3

P4

S1

Sistemas DigitalesMg. Juan Carlos Gonzales Suárez

Funciones Lógicas

X Y

P1

P2

P3

P4

S1

F = Suma de Productos = Σ ( minterm)

Matriz AND

Matriz OR

• Sustituyen a circuitos SSI y MSI.• Ahorran espacio y reducen coste y número de

dispositivos.• Formados por Matrices fijas o programables.• 1960: matriz programable más antigua. Matriz de

diodos.• Puertas AND y OR conectadas a una matriz

programable. Uso fusibles programables una vez.

Sistemas DigitalesMg. Juan Carlos Gonzales Suárez

Programmable Logic Device - PLD

MatrizFusibles

AND

MatrizFusibles

OR

Variablesde

EntradaSalida

PLA ProgrammableLogicArray

Tipos de PLD

Sistemas DigitalesMg. Juan Carlos Gonzales Suárez

MatrizANDFija

MatrizOR

Program.

Variablesde

EntradaSalida

PROM ProgrammableReadOnlyMemory

MatrizAND

Program.

MatrizOR

Program.

Variablesde

EntradaSalida

PLD

Sistemas DigitalesMg. Juan Carlos Gonzales Suárez

PAL ProgrammableArrayLogic

GAL GenericArrayLogic

MatrizAND

Program.

MatrizOR Fija

+Lógica de

Salida

Variablesde

EntradaSalida

MatrizAND

Program.

MatrizOR Fija

+Lógica de

SalidaProgram.

Variablesde

EntradaSalida

Sistemas DigitalesMg. Juan Carlos Gonzales Suárez

PLD - Programmable Logic DeviceX Y Z

P1

P2

P3

P4

S1 S2

OR Plane

AND Plane

Sistemas DigitalesMg. Juan Carlos Gonzales Suárez

PLD - Programmable Logic DeviceX Y Z

P1

P2

P3

P4

S1 S2

Sistemas DigitalesMg. Juan Carlos Gonzales Suárez

CPLD : Complex Programmable Logic Device

Bloques lógicos SPLD (LB) interconectados a través de otro bloque programable (PIM)

y con bloques de interfaz con el exterior (IOB)

Sistemas DigitalesMg. Juan Carlos Gonzales Suárez

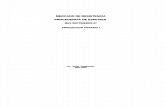

Diferencias entre CPLDs y FPGAs

CPLD FPGA

Numero equivalente de FlipFlops

128 4000

Numero equivalentes de GALs 22V10

13 400

Elementos Lógicos Hasta 500 Hasta 250,000

Voltaje de Operación 5Voltios 3.3V externo, 1.5V interno

Costo mínimo $10 $15

Empaquetado Alguno definidos SMT (Surface Mount Technology

Retención de Programación

Yes No – se carga el programa al energizar

Sistemas DigitalesMg. Juan Carlos Gonzales Suárez

Antifusibles: dispositivos de dos terminales de resistencia muy elevada antes de ser programados. Al programarlos, esa resistencia disminuye.

Programación: se perfora el aislante con lo que las dos líneas conductoras quedan conectadas. Se programa para establecer las conexiones,mientras que en las PAL se actúa para eliminarlas, de ahí el nombre.

Sistemas DigitalesMg. Juan Carlos Gonzales Suárez

Diseño con PLDs

Simulador Compilador

Grabadorde PLDs

Problema de Diseño

PAL22V10

JEDEC: JointElectronicDeviceEngineeringCouncil

Sistemas DigitalesMg. Juan Carlos Gonzales Suárez

Programa que describe hardwareName MUX;Partno ;Revision 01;Date 8/10/99;Designer PLD Expert;Company Atmel Corp.;Location None;Assembly None;Device p22V10;

/* MUX de 2 a 1 *//** Inputs **/pin [3,4] = [a, b];pin 5 = s;

/** Outputs **/pin 23 = y;

Cabecera

Pines de Entrada y Salida

Programa/** Función Mux 2 a 1 **/y = (a & (s:0)) # (b & (s:1));

Mux de

2 a 1

a =>

b =>

s =>

Þ y

Sistemas DigitalesMg. Juan Carlos Gonzales Suárez

Parte de un archivo JEDEC

‘1’ fuse blown

‘0’ fuse intact

Numero de Fusible

Comentario