CPU08

Click here to load reader

-

Upload

william-mosquera -

Category

Documents

-

view

198 -

download

1

Transcript of CPU08

CPU08

Características y modelo de programación.

Revisión 1.0 de Enero de 2006.

CPU08 – Características y modelo de programación.

Índice:Características mas relevantes y recursos disponibles de la CPU08....................................................4

Características de la CPU: ..............................................................................................................4Modelo de programación de la CPU:..............................................................................................4

Estructura de la CPU08........................................................................................................................4Registros de la CPU08..........................................................................................................................5Modos de direccionamiento de la CPU08............................................................................................8Juego de instrucciones de la CPU08...................................................................................................13Interrupciones en la CPU08................................................................................................................18

Pag. 2 de 17

CPU08 – Características y modelo de programación.

Características mas relevantes y recursos disponibles de la CPU08.

Características de la CPU:

● Código objeto totalmente compatible con la familia MC68HC05. ● Puntero de Pila (Stack Pointer) de 16 bits. ● Registro índice de 16 bits con instrucciones de manipulación de dicho registro. ● Frecuencia interna de bus de 8 MHz. ● 64 Kbytes de memoria para datos y programas. ● 16 modos de direccionamiento. ● Posibilidad de transferencia de datos memoria-memoria sin utilizar el acumulador. ● Instrucción de multiplicación rápida de 8 x 8 bits. ● Instrucción de división rápida de 16 para 8 bits. ● Instrucciones BCD. ● Modos STOP y WAIT disponibles.

Modelo de programación de la CPU:

● Acumulador de 8 bits. ● Registro índice de 16 bits. ● Puntero de pila de 16 bits. ● Contador de programa de 16 bits. ● Registro de código de condición de 8 bits.

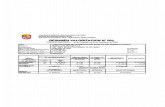

Estructura de la CPU08.

La estructura funcional de la CPU08 se divide en:

● Unidad de Control. Consiste en una máquina de estados finitos que controla el funcionamiento de la Unidad de Ejecución mediante las señales de control.

● Unidad de Ejecución, que a su vez consta de:

● Unidad Aritmético-Lógica. La ALU permite el cálculo aritmético-lógico necesario para llevar a cabo la ejecución de las distintas instrucciones que así lo precisen.

● Registros. Almacenamiento temporal de operandos, resultados, direcciones, estado de la máquina...

● Buses. Mediante los cuales se comunica con el resto de módulos del microcontrolador.

Pag. 3 de 17

CPU08 – Características y modelo de programación.

Estructura de la CPU08.

Registros de la CPU08.

ACUMULADOR (A).

El acumulador es un registro de propósito general de 8 bits usado por la CPU para guardar temporalmente los operandos y resultados de las operaciones realizadas.

REGISTRO INDICE (H:X).

Es un registro de 16 bits que permite al usuario acceder a los 64 Kbytes del mapa de memoria mediante direccionamiento indexado. Consta de dos registros de 8 bits, el H y X, que concatenados forman el H:X de 16 bits siendo H el alto y X el bajo.

También se puede utilizar como registro temporal de datos.

PUNTERO DE PILA (STACK POINTER, SP).

Es un registro de 16 bits que contiene la dirección de la próxima posición de memoria a utilizar por la pila. Esta dirección es decrementada cuando un dato es metido en la pila, apuntando entonces a la siguiente posición (vacante). Se incrementa cuando un dato es sacado de la pila, pasando entonces la posición anteriormente apuntada a estar vacante. También es posible utilizar es registro de Stack Pointer como registro índice para acceder temporalmente a las variables contenidas en la pila. La CPU utiliza el contenido de este registro

Pag. 4 de 17

UNIDAD DECONTROL

UNIDADARIMETICO

LÓGICA

7

07815

07815

0

07815

CZNIH11V

Acumulador (A)

Registro Índice (H:X)

Puntero de pila (SP)

Contador de programa (PC)

Registro de códigos de condición (CCR)

Bus de datos

Bus de direcciones

EstadoControl

Ind. desbordamiento complemento a dos Indicador de acarreo medio

Máscara de interrupción

Indicador de acarreo Indicador de resultado 0 Indicador de resultado negativo

CPU08

CPU08 – Características y modelo de programación.

para calcular la dirección efectiva de la variable buscada. Se puede utilizar como índice de 8 bits o 16 bits.

Un reset de la CPU provoca que el Stack Pointer se posicione en 0x00FF pudiendo ser recolocada posteriormente en cualquier zona de la memoria RAM.

El siguiente gráfico muestra el crecimiento de la pila cuando se guardan datos en ella:

Utilizando la lógica contraria en el caso de decrecimiento de la pila.

CONTADOR DE PROGRAMA (PC).

Es un registro de 16 bits que contiene la dirección de la próxima instrucción a ejecutar u operando a utilizar. Normalmente esta dirección se obtiene por incremento automático del contador de programa, pero instrucciones de salto, bifurcaciones o las propias interrupciones pueden romper esta secuencia cargando el registro con la dirección de la próxima instrucción a ejecutar.

El RESET provoca que el contador de programa se cargue con el contenido del vector de RESET, que se encuentra en las direcciones 0xFFFE Y 0xFFFF. La dirección representada por el vector de RESET contendrá la primera instrucción a ejecutar por la CPU.

REGISTRO DE CÓDIGOS DE CONDICIÓN (CCR).

Es un registro de 8 bits de los cuales 6 son significativos. Contiene el bit de mascara de interrupción y cinco Indicadores que indican el resultado de la última instrucción ejecutada. Son los siguientes:

● Indicador de desbordamiento (V).

La CPU pone a 1 este indicador cuando se genera un desbordamiento de complemento a dos como resultado de una operación aritmética. Este indicador se utiliza por algunas instrucciones de bifurcación como BGT (bifurca si mayor que), BGE (bifurca si mayor o igual que), BLE (bifurca si menor o igual que), BLT (bifurca si menor que).

● Indicador de acarreo medio (H).

Pag. 5 de 17

A

H

VACANTE

VACANTE

0xFF

0xFE

0xFD

0xFC

Se produce un RESET (SP=0xFF)

PSHA, se guarda A en la pila (0xFF) y se decrementa SP (SP=0xFE)

PSHH, se guarda H en la pila (0xFE) y se decrementa SP (SP=0xFD)

La pila decrece hacia las direcciones inferiores y crece hacia las direcciones superiores

STACK POINTER

CPU08 – Características y modelo de programación.

La CPU pone a 1 este indicador cuando se produce un acarreo entre los bits 3 y 4 del acumulador en una suma sin acarreo (ADD) o en una suma con acarreo (ADC). Este indicador es utilizado en operaciones aritméticas BCD. La instrucción DAA (ajuste decimal del acumulador) utiliza el estado de los indicadores H y C para determinar el factor de corrección apropiado.

● Máscara de interrupción (I).

Cuando está a 1, las interrupciones están deshabilitadas y habilitadas en caso contrario. Cuando se produce una interrupción, la máscara de interrupción es puesta a 1 automáticamente después de que los registros de la CPU son salvados en la pila pero antes de ser lanzada la interrupción. Con esto se consigue que no se produzcan interrupciones anidadas a no ser que el usuario modifique el estado de la mascara a 0 durante la ISR para permitirlas. Si se produce una interrupción mientras la máscara de interrupción está a 1, la petición de interrupción es guardada y será lanzada, por orden de prioridad entre las pendientes, cuando el servicio de la interrupción actual finaliza.

● Indicador de resultado negativo (N).

La CPU pone a 1 este indicador cuando una operación aritmética, operación lógica o una modificación de datos produce un resultado negativo.

● Indicador de resultado cero (Z).

La CPU pone a 1 este indicador cuando una operación aritmética, operación lógica o una modificación de datos produce el resultado 0x00.

● Indicador de acarreo (C).

La CPU pone a 1 este indicador cuando una operación de suma o resta produce un acarreo mas allá del séptimo bit del acumulador. Algunas operaciones lógicas e instrucciones de transformación de datos también modifican el indicador de acarreo.

Modos de direccionamiento de la CPU08.

La CPU08 utiliza 16 modos de direccionamiento diferentes para poder acceder a los datos.

Estos modos de direccionamiento definen como la CPU busca los datos requeridos para poder ejecutar una instrucción. Estos son:

1. INHERENTE.

El direccionamiento inherente es utilizado en instrucciones donde el operando a tratar se encuentra implícito en el código de la instrucción.La mayoría de estas instrucciones tienen una longitud de 1 byte.

Pag. 6 de 17

CPU08 – Características y modelo de programación.

Ejemplos:PULA, CLRA, TXA, INCA... ;Empila, borra, transfiere, incrementa... el acumulador.

2. INMEDIATO.

En las instrucciones con direccionamiento inmediato, el operando está contenido en el(los) byte(s) siguiente(s) al código de operación de la instrucción. Estos bytes representan el propio valor del operando. El operando tiene una longitud de 1 o 2 bytes.

Ejemplos:SUB #$22 ;Resta el valor inmediato $22 al acumulador.

AIX #1 ;Suma el valor 1 al registro H:X.

3. DIRECTO.

Se utiliza el direccionamiento directo para acceder a los primeros 256 bytes (página directa o página 0) del mapa de memoria mediante solo un byte de dirección. Se asume el byte alto de la dirección efectiva como 0x00. Este método de direccionamiento da lugar a instrucciones mas cortas (2 bytes, uno para el opcode y otro para la dirección) reduciendo el espacio de memoria ocupado y el tiempo de ejecución.

Ejemplos:LDA 0x02 ;Carga en el acumulador el valor del la pos. de memoria

;0x02. STA 0x01 ;Y posteriormente lo guarda en la pos. de memoria 0x01.

En ambos casos, las direcciones se representan mediante operandos de 1 byte.

4. EXTENDIDO.

Se utiliza el direccionamiento extendido para poder acceder a cualquiera de los 64 Kbytes del mapa de memoria mediante dos bytes de dirección. Las instrucciones que utilizan este direccionamiento tienen una longitud de 3 bytes, el primero para el código de operación y el segundo y tercero para el byte mas y menos significativo de la dirección de memoria. Se utiliza este método de direccionamiento cuando la dirección requerida está fuera de la página directa (o página 0).

Ejemplos: LDA 0x8000 ;Carga en el acumulador el valor de la pos. de memoria

;0x8000.

Pag. 7 de 17

CPU08 – Características y modelo de programación.

STA 0x100 ;Y posteriormente lo guarda en la pos. de memoria 0x100.

5. INDEXADO, SIN OFFSET.

Los direccionamientos indexados utilizan el registro índice como puntero que contiene la (o parte de la) dirección del operando a tratar. El direccionamiento indexado sin offset se utiliza para acceder a cualquiera de los 64 Kbytes del mapa de memoria mediante instrucciones de solo 1 byte de longitud. Para obtener la dirección de memoria requerida se utiliza el registro índice H:X, donde H contiene el byte mas significativo y X el menos significativo.

Ejemplos:LDA ,X ;Carga en el acumulador el valor de la pos. apuntada por el

;registro H:X.INCX ;Actualiza el registro índice.STA ,X ;Guarda el valor del acumulador en la pos. apuntada por el

;nuevo valor en H:X.

6. INDEXADO, CON OFFSET DE 8 BIT.

El direccionamiento indexado con offset de 8 bit se utiliza para acceder a cualquiera de los 64 Kbytes del mapa de memoria mediante instrucciones de 2 bytes de longitud. Para obtener la dirección de memoria requerida se utiliza el registro índice H:X mas el offset de 8 bits (1 byte) que sigue al código de operación. La CPU suma estos valores para obtener la dirección efectiva.

Ejemplos:LDA off8bit,X ;Carga en el acumulador el valor de la pos. apuntada por H:X

;+ off8bit.NCX ;Actualiza el registro índice.STA off8bit,X ;Guarda el valor del acumulador en la pos. apuntada por H:X

;+ off8bit.

7. INDEXADO, CON OFFSET DE 16 BIT.

El direccionamiento indexado con offset de 16 bit se utiliza para acceder a cualquiera de los 64 Kbytes del mapa de memoria mediante instrucciones de 3 bytes de longitud. Para obtener la dirección de memoria requerida se utiliza el registro índice H:X mas el offset de 16 bits (2 bytes) que sigue al código de operación. La CPU suma estos valores para obtener la dirección efectiva.

Ejemplos:LDA off16bit,X ;Carga en el acumulador el valor de la pos. apuntada por H:X

;+ off16bit.INCX ;Actualiza el registro índice.

Pag. 8 de 17

CPU08 – Características y modelo de programación.

STA off16bit,X ;Guarda el valor del acumulador en la pos. apuntada por H:X ;+ off16bit.

8. STACK POINTER, CON OFFSET DE 8 BIT.

Los direccionamientos indexados mediante Stack Pointer utilizan el registro SP como puntero que contiene la (o parte de la) dirección del operando a tratar. El direccionamiento mediante Stack Pointer con offset de 8 bit se utiliza para acceder a cualquiera de los 64 Kbytes del mapa de memoria mediante instrucciones de 3 bytes de longitud. Para obtener la dirección de memoria requerida se utiliza el registro SP mas el offset de 8 bits (1 byte) que sigue al código de operación (2 bytes). La CPU suma estos valores para obtener la dirección efectiva.

Ejemplos:LDA off8bit,SP ;Carga en el acumulador el valor de la pos. apuntada por SP

;+ off8bit.TXS ;Actualiza el registro SP.STA off8bit,SP ;Guarda el valor del acumulador en la pos. apuntada por SP

;+ off8bit.

9. STACK POINTER, CON OFFSET DE 16 BIT.

El direccionamiento mediante Stack Pointer con offset de 16 bit se utiliza para acceder a cualquiera de los 64 Kbytes del mapa de memoria mediante instrucciones de 4 bytes de longitud. Para obtener la dirección de memoria requerida se utiliza el registro SP mas el offset de 16 bits (2 byte) que sigue al código de operación (2 bytes). La CPU suma estos valores para obtener la dirección efectiva.

Ejemplos:LDA off16bit,SP ;Carga en el acumulador el valor de la pos. apuntada por SP

;+ off16bit.TXS ;Actualiza el registro SP.STA off16bit,SP ;Guarda el valor del acumulador en la pos. apuntada por SP

;+ off16bit.

10. RELATIVO.

El direccionamiento relativo se utiliza en las bifurcaciones condicionales para obtener la dirección efectiva de la próxima instrucción a ejecutar (salto). La CPU calcula la dirección de destino sumando al contador de programa actual (siguiente al salto) el valor del byte que sigue al código de operación de la instrucción. Este valor de desplazamiento se codifica mediante un byte complemento a dos lo que permite un rango de salto de -128 a 127 bytes.

Ejemplos:

Pag. 9 de 17

CPU08 – Características y modelo de programación.

CMP #7 ;Compara el valor guardado en el acumulador con 7.BEQ SIGUE ;Y si es igual salta a la dirección SIGUE.

11. MEMORIA A MEMORIA, INMEDIATO A DIRECTO.

Este direccionamiento permite mover un valor inmediato a una posición perteneciente a la página 0 (0x00 - 0xFF) sin que tenga que almacenarse temporalmente en el acumulador. El primer operando después del código de operación es el valor inmediato, el segundo byte la dirección de la página 0 donde será almacenado. Este direccionamiento es útil para inicializar variables y registros que están ubicados en la página 0.

Ejemplos:MOV #0,$40 ;Inicializa la dirección 0x40 a 0.

12. MEMORIA A MEMORIA, DIRECTO A DIRECTO.

Este direccionamiento permite mover contenidos entre posiciones de la página 0 sin que tenga que almacenarse temporalmente en el acumulador. El primer operando después del código de operación es la dirección de origen y el segundo operando es la dirección de destino.

Ejemplos:MOV $40,$80 ;Mueve el valor almacenado en la dirección 0x40 a la 0x80.

13. MEMORIA A MEMORIA, INDEXADO A DIRECTO CON POST-INCREMENTO.

Este direccionamiento permite mover el valor contenido en la posición apuntada por H:X a otra posición dentro de la página 0 sin que tenga que almacenarse temporalmente en el acumulador. El operando después del código de operación es la dirección de destino. Después se incrementa el registro índice.

Ejemplos:MOV X+,$20 ;Mueve el valor apuntado en H:X a la dirección 0x20.

14. MEMORIA A MEMORIA, DIRECTO A INDEXADO CON POST-INCREMENTO.

Este direccionamiento permite mover el valor contenido en una posición de la página 0 a otra posición apuntada por el registro H:X sin que tenga que almacenarse temporalmente en el acumulador. El operando después del código de operación es la dirección de origen. Después se incrementa el registro índice.

Pag. 10 de 17

CPU08 – Características y modelo de programación.

Ejemplos: MOV $20,X+ ;Mueve el valor almacenado en 0x20 a la posición apuntada

;por H:X.

15. INDEXADO CON POST-INCREMENTO.

Se trata de un direccionamiento indexado mediante índice H:X sin offset. El índice apunta al operando a tratar con posterior incremento para apuntar al siguiente valor. Lo utilizan instrucciones de comparación para realizar búsquedas de datos en tablas lineales, si se encuentra el valor buscado se bifurca a la dirección dada mediante direccionamiento relativo.

Ejemplos:BUSQ CBEQ X+,ENC ;Compara el valor apuntado por H:X con el

;acumulador y si es igual salta a ENC. BRA BUSQ ;En caso contrario, sigue buscando.

16. INDEXADO CON OFFSET DE 8 BIT Y POST-INCREMENTO.

Se trata de un direccionamiento indexado mediante índice H:X con offset de 8 bits. El índice apunta al operando a tratar con posterior incremento para apuntar al siguiente valor. Lo utilizan instrucciones de comparación para realizar búsquedas de datos en tablas lineales, si se encuentra el valor buscado se bifurca a la dirección dada mediante direccionamiento relativo.

Ejemplos: BUSQ CBEQ $20,X+,ENC ;Compara el valor apuntado por (H:X + 0x20) con el ;acumulador y si es igual salta a ENC. BRA BUSQ ;En caso contrario, sigue buscando.

Pag. 11 de 17

CPU08 – Características y modelo de programación.

Juego de instrucciones de la CPU08.

El juego de instrucciones de la CPU08 se puede dividir en las siguientes categorías:

● Instrucciones aritméticas.

ADD Suma sin acarreo sobre el acumulador.

ADCSuma con acarreo sobre el acumulador.

DAA Ajuste decimal del acumulador.

SUB Resta sin acarreo al acumulador.

SBC Resta con acarreo al acumulador.

MUL Multiplicación.

DIV División.

● Instrucciones de movimiento de datos.

LDA Carga acumulador desde la memoria

LDX Carga registro X desde la memoria.

STA Guarda el contenido del acumulador en memoria.

STX Guarda el contenido del registro X en memoria.

LDHX Carga registro H:X desde la memoria.

STHX Guarda el contenido del registro H:X en memoria.

TXA Transfiere el contenido del registro X al acumulador.

TAX Transfiere el contenido del acumulador al registro X.

PSHA Empila acumulador.

PSHH Empila registro H.

PSHX Empila registro X.

PULA Desempila acumulador.

PULH Desempila registro H.

PULX Desempila registro X.

MOVMueve memoria-memoria e inmediato-memoria sin utilizar el acumulador.

TAP Transfiere el contenido del acumulador al registro CCR.

TPA Transfiere el contenido del registro CCR al acumulador.

TSX Transfiere el contenido del registro SP al registro H:X.

TXS Transfiere el contenido del registro H:X al registro SP.

● Instrucciones de modificación de bytes.

INCA Incrementa en 1 el valor del acumulador.

INCX Incrementa en 1 el valor del registro X.

INC Incrementa en 1 sobre memoria.

Pag. 12 de 17

CPU08 – Características y modelo de programación.

DECA Decrementa en 1 el valor del acumulador.

DECX Decrementa en 1 el valor del registro X.

DEC Decrementa en 1 sobre memoria.

CLRA Pone a 0 el acumulador.

CLRX Pone a 0 el registro X

CLRH Pone a 0 el registro H

CLR Pone a 0 una posición de memoria.

AIS Suma un valor inmediato con signo al registro SP.

AIX Suma un valor inmediato con signo al registro índice.

NEGA Niega el acumulador (complemento a dos).

NEGX Niega el registro X (complemento a dos).

NEGNiega una posición de memoria (complemento a dos).

● Instrucciones de modificación de bits.

BSET Pone a 1 el bit indicado en una posición de memoria.

BCLR Pone a 0 el bit indicado en una posición de memoria.

● Instrucciones de rotación/desplazamiento.

LSLA Desplazamiento lógico a la izquierda del contenido del acumulador.

LSLX Desplazamiento lógico a la izquierda del contenido del registro X.

LSL Desplazamiento lógico a la izquierda del contenido de una posición de memoria.

LSRA Desplazamiento lógico a la derecha del contenido del acumulador.

LSRX Desplazamiento lógico a la derecha del contenido del registro X.

LSR Desplazamiento lógico a la derecha del contenido de una posición de memoria.

ASLA Desplazamiento aritmético a la izquierda del contenido del acumulador.

ASLX Desplazamiento aritmético a la izquierda del contenido del registro X.

ASL Desplazamiento aritmético a la izquierda del contenido de una posición de memoria.

ASRA Desplazamiento aritmético a la derecha del contenido del acumulador.

ASRX Desplazamiento aritmético a la derecha del contenido del registro X

ASR Desplazamiento aritmético a la derecha del contenido de una posición de memoria.

ROLARotación a la izquierda a través del indicador de acarreo del contenido del acumulador.

ROLX Rotación a la izquierda a través del indicador de acarreo del contenido del registro X.

ROLRotación a la izquierda a través del indicador de acarreo del contenido de una posición de memoria.

RORARotación a la derecha a través del indicador de acarreo del contenido del acumulador.

RORX Rotación a la derecha a través del indicador de acarreo del contenido del registro X

Pag. 13 de 17

CPU08 – Características y modelo de programación.

RORRotación a la derecha a través del indicador de acarreo del contenido de una posición de memoria.

● Instrucciones lógicas.

AND Y lógico sobre el contenido del acumulador.

ORA O lógico sobre el contenido del acumulador.

EOR O-Exclusivo lógico sobre el contenido del acumulador.

COMA Complemento del contenido del acumulador (complemento a 1).

COMX Complemento del contenido del registro X (complemento a 1).

COMComplemento del contenido de una posición de memoria (complemento a 1).

NSA Intercambio de los bits 0-3 por los bits 4-7 del acumulador.

● Instrucciones de test.

CMP Compara el contenido del acumulador con la memoria.

CPX Compara el contenido del registro X con la memoria.

CPHX Compara el contenido del registro índice con la memoria (2 bytes).

BITCompara (mediante Y lógico a todos sus bits) el contenido del acumulador con la memoria.

TSTA Prueba el signo y valor (igual o distinto de 0) del contenido del acumulador.

TSTX Prueba el signo y valor (igual o distinto de 0) del contenido del registro X.

TST Prueba el signo y valor (igual o distinto de 0) del contenido de la memoria.

BRCLR Bifurca si el bit especificado en la posición de memoria dada es 0.

BRSET Bifurca si el bit especificado en la posición de memoria dada es 1.

● Instrucciones de bifurcación y salto.

JMP Salto.

JSR Salto a subrutina.

RTS Retorno desde subrutina.

BRA Bifurca siempre.

BCC Bifurca si el indicador de acarreo (C) es 0.

BCS Bifurca si el indicador de acarreo (C) es 1.

BEQ Bifurca si igual.

BGE Bifurca mayor o igual que (con signo).

BGT Bifurca si mayor que (con signo).

BHCC Bifurca si el indicador de acarreo medio (H) es 0.

BHCS Bifurca si el indicador de acarreo medio (H) es 1.

BHI Bifurca si mayor que.

BHS Bifurca si mayor o igual que.

BIH Bifurca si IRQ está activa.

Pag. 14 de 17

CPU08 – Características y modelo de programación.

BIL Bifurca si IRQ está desactiva.

BLE Bifurca si menor o igual que (con signo).

BLO Bifurca si menor.

BLS Bifurca si menor o igual.

BLT Bifurca si menor que (con signo).

BMC Bifurca si el indicador de máscara de interrupción (I) es 0.

BMI Bifurca si menor.

BMS Bifurca si el indicador de máscara de interrupción (I) es 1.

BNE Bifurca si diferente.

BPL Bifurca si mayor.

BRN Bifurca nunca.

BSR bifurca a subrutina.

CBEQ Compara el contenido del acumulador con memoria y bifurca si igual.

CBEQACompara el contenido del acumulador con inmediato y bifurca si igual.

CBEQX Compara el contenido del registro X con inmediato y bifurca si igual.

DBNZ Decrementa el contenido de la memoria y bifurca si es distinto de 0.

DBNZA Decrementa el contenido del acumulador y bifurca si es distinto de 0.

DBNZX Decrementa el contenido del registro X y bifurca si es distinto de 0.

● Instrucciones de control.

CLC Borra el indicador de acarreo (C=0).

CLI Borra el indicador de máscara de interrupción (I=0).

SEC Activa el indicador de acarreo (C=1).

SEI Activa el indicador de máscara de interrupción (I=1).

SWI Interrupción software.

RTI Retorno de interrupción.

RSP Reset puntero de pila (SP=0xff).

NOP No hace nada, gasta 1 ciclo de bus.

WAIT Habilita interrupciones y detiene CPU hasta próxima interrupción.

STOP Habilita interrupciones y para CPU.

Pag. 15 de 17

CPU08 – Características y modelo de programación.

Interrupciones en la CPU08.

La CPU08 ejecuta instrucciones de forma secuencial pero en algunas ocasiones es necesario la ejecución de un conjunto de instrucciones como respuesta a un evento externo. Estos eventos suelen presentarse de forma asíncrona durante la ejecución del programa principal y requieren que sean atendidos mediante una rutina de servicio a interrupción (ISR) apropiada.

Las interrupciones son el medio para suspender la ejecución normal del programa. La CPU08 puede procesar 128 fuentes de interrupción incluyendo la interrupción software (SWI).

Las interrupciones son generadas por los distintos módulos periféricos del microcontrolador y son reconocidas, siempre que el bit de máscara de interrupción esté deshabilitado, de acuerdo a su nivel de prioridad. El módulo periférico indica a la CPU su condición mediante un indicador de interrupción pendiente. Cuando la ISR sirve la interrupción, el indicador del módulo periférico debe ser borrado.

Una interrupción pendiente es reconocida durante el último ciclo de la instrucción en curso siempre y cuando ésta se haya generado antes de este ciclo. Las que se generan durante el último ciclo de una instrucción no son reconocidas hasta el último ciclo de la siguiente instrucción. Cuando una interrupción es reconocida, el código de operación de la instrucción SWI es cargado en el registro de instrucción de la CPU, siento entonces la próxima instrucción a ejecutar.

Antes de comenzar a ejecutar la rutina de servicio de interrupción, la CPU debe de salvar el estado de la máquina para poder retornar a éste cuando la interrupción sea servida. Para ello, la CPU debe guardar sus registros en la pila (todos menos el H que no se empila para mantener la compatibilidad con su antecesora CPU05). Los registros empilados y su orden son: PC, X, A y CCR, que son desempilados en orden inverso. Es importante destacar que el bit I (máscara de interrupción) es activado (I=1, y por lo tanto las interrupciones inhibidas) después de empilar el registro CCR por lo que el estado guardado en el CCR es el del programa principal.

Todas las interrupciones tienen asignado un nivel de prioridad lo que permite, ante un conflicto por petición múltiple, servir antes la que tenga la prioridad mas alta. El módulo encargado de arbitrar y lanzar las interrupciones es el SIM. Una vez que una interrupción está siendo servida ninguna otra interrupción la puede interrumpir (independientemente de su prioridad) a no ser que el bit de máscara de interrupción (I) sea desactivado (I=0).

Cuando una interrupción ha sido servida, la instrucción RTI termina el proceso de interrupción y retorna al punto donde el programa principal fue interrumpido. Para ello, debe devolver a la CPU al estado de máquina anterior a la interrupción restaurando los valores de los registros previamente guardados en la pila.

La CPU08 cuenta con 128 posibles vectores de interrupción, contando el RESET y SWI:

Pag. 16 de 17

CPU08 – Características y modelo de programación.

DIRECCIÓN INTERRUPCIÓN PRIORIDAD

FFFE RESET 1

FFFC SWI 2

FFFA IREQ[0] 3

.

...

.

.

FF02 IREQ[124] 127

FF00 IREQ[125] 128

aunque los microcontroladores no suelen utilizar todas las interrupciones disponibles.

Pag. 17 de 17