MIRTA VARGAS DE ARGENTINA MEDIA 9 CALZADA Cat B 2° grupo 1ª Actividad

AUTOPOLARIZACION

-

Upload

maguito148 -

Category

Documents

-

view

4 -

download

1

description

Transcript of AUTOPOLARIZACION

Universidad Nacional de PiuraFacultad de Ing. IndustrialEscuela de Ing. Mecatrnica

Prctica de Laboratorio 01

Tema:Polarizacin del Transistor FET

Curso:Circuitos Electrnicos II

Docente:Ing. Shlomi Caldern

Autores:Chvez Gambini Ral AurelioGamarra Guarnizo Luis AlbertoJimnez Ruz Roger HumbertoRamrez Mrquez Fernando Rafael

Piura _ Per

2014

POLARIZACION DEL FETI.-OBJETIVOSVerificar el funcionamiento de un JFETExperimentar circuitos de polarizacin del JFETII.-FUNDAMENTO TEORICOEn los transistores bipolares, una pequea corriente de entrada (corriente de base) controla la corriente de salida (corriente de colector); en los casos de los FET, es un pequeo voltaje de entrada que controla la corriente de salida.La corriente que circula en la entrada es generalmente despreciable (menos de un pico amperio). Esto es una gran ventaja, cuando la seal proviene de un dispositivo tal como un micrfono de condensador o un transductor piezo elctrico, los cuales proporcionan corrientes insignificantes.Los FETs, bsicamente son de dos tipos:- El transistor de efecto de campo de Juntura o JFET.- El transistor de efecto de campo con compuerta aislada o IGFET, tambin conocido como semiconductor de xido de metal, MOS, o simplemente MOSFET.EL JFET

El JFET esta constituido por una barra de silicio tipo N o canal N, introducido en una barra o anillo de silicio tipo P tal como se muestra en la Fig. ALos terminales del canal N son denominados SURTIDOR (SOURCE) y DRENADOR (DRAIN). El anillo forma el tercer terminal del JFET llamado COMPUERTA (GATE).Inicialmente circula una corriente por la compuerta, pero posteriormente la corriente circula nicamente desde el surtidor al Drenador sin cruzar la juntura PN.

El control de esta corriente se efecta por medio de la aplicacin de un voltaje de polarizacin inverso, aplicado entre la compuerta y el surtidor (VGS), formando un campo elctrico el cual limita el paso de la corriente a travs del canal N (Fig.B). Al aumentar el voltaje inverso, aplicado a la compuerta, aumenta el campo elctrico, y la corriente de Surtidor a Drenador disminuye.Tambin se construyen JFETs con barra de silicio tipo P y anillos de silicio tipo N, denominndose JFET canal P.El voltaje aplicado entre el Drenador y el Surtidor (VDS), no debe sobrepasar el voltaje de ruptura (tpicamente 50V) porque destruira el dispositivo.Si se aplica polarizacin directa a la compuerta, circular una alta corriente por la compuerta que puede destruir el JFET si no esta limitada por una resistencia en serie con la compuerta.VALORES COMERCIALES PARA EL JFET

Voltaje VDS (V)25,30,40,50

Potencia (W)0.15,0.3,1.8,30

Para comprar un JFET se debe indicar su cdigo.PRUEBA DEL JFETSe comprueba con un ohmmetro en la escala de Rx1 Rx10.Entre compuerta y surtidor o compuerta y Drenador debe marcar como si fuera un diodo de silicio; es decir alta resistencia en un sentido y baja en el inverso.Entre Drenador y surtidor, el valor hmico exclusivamente del material del canal. Su valor vara entre 2K y 10K, siendo el mismo en ambos sentidos.III.-EQUIPO Y MATERIALESDos fuentes de voltaje ajustables de 0 a 15 V.Un transistor 2N3904Un multitester digital o analgicoUn JFET K373Un LED de color (verde, rojo o amarillo)Resistores W: de 270 , 470, 33K, 4.7K, 100K, 1.8K, 2K, 1M.Potencimetro de 10K.

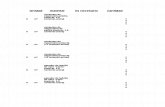

EXPERIMENTACIN:1. Para la sesin de laboratorio se utiliz un transistor JFET 2SK170.VdsId

0.41.32

0.92.68

1.33.79

1.44.32

25.63

2.56.25

36.48

3.36.56

46.68

4.56.76

5.16.83

5.96.9

87.03

10.17.13

2. En primer lugar se realizaron mediciones para conocer las caractersticas del transistor, es decir encontrar su corriente de saturacin y su voltaje de estrangulamiento. Para encontrar estos valores se realiz la curva caracterstica del transistor, cuando el voltaje compuerta fuente es de cero voltios, obteniendo los siguientes resultados:

Con estos valores se pudo trazar la curva caracterstica del JFET 2SK170:

3. A continuacin se implementaron los siguientes circuitos en protoboard:

Y se las mediciones de Vds, Vgs, Vgd, Is, Id, Ig, mostradas a continuacin.

MagnitudValor Medido

Vds8.02 v

Vgs0 v

Vgd8.03 v

Is6 mA

Id7.12 mA

Ig0 mA

FIG.2.RESULTADOS PARA LA FIG. 1AEn el circuito de la FIG. 1B, a travs del potencimetro se hizo variar el voltaje Vgs a valores cada vez ms negativos, e ir observando la corriente del drenaje. Con el fin de encontrar el Vgs que hiciera que nuestra corriente de drenaje se redujera a 0 amperes, este valor de Vgs seria nuestro voltaje de estrangulamiento. Se obtuvieron los siguientes resultados:MagnitudValor Medido

Vds8.4

Vgs-3.3

Vgd10

Is0

Id0

Ig0

FIG.2.RESULTADOS PARA LA FIG. 1BAnalizando los resultados de ambos cuadros, se deduce que la corriente de saturacin es de 7.13 mA y el voltaje de estrangulamiento es de -3.3 voltios.

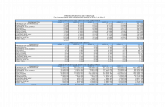

AUTOPOLARIZACINArme el circuito mostrado. Conecte adecuadamente los instrumentos para medir ID y VGS, encienda las fuente y anote los valores de ID, VGS y las dems tensiones del circuito.Todo circuito debe ser armado con las fuentes apagados previamente ajustadas al valor dado en el diagrama.

Los resultados se muestran en la siguiente tabla:MAGNITUDVALOR MEDIDOVALOR CALCULADO

VDS5 V5.23 V

VGS-0.6 V- 0.65 V

VGD5.4 V5.86 V

IS2 mA2.3 mA

ID2.3 mA2.3 mA

IG0 mA0 mA

VALORES TEORICOS CALCULADOSVGS = - ID . RSEligiendo ID = 4 mATenemos : VGS = - (4 mA)(270)VGS = - 1.1 VEstos dos datos nos permiten graficar y mediante la superposicin de grficas se obtienen los siguientes datos:IDQ = 2.3 mAVGSQ = - 0.65 VTenemos adems que ID = ISVDS = 10V (ID) (RD+ RS)VDS = 10V (2.3 mA) (1800+270)VDS = 5.23 VVD = 10V (2.3 mA) (1800)VD = 5.86 VVG = 0VVGD = VD VG = 5.86 V 0 = 5.86 V

POLARIZACION POR DIVISOR DE TENSIONArme el circuito mostrado y haga las medidas de ID as como las tensiones en los diferentes nudos y puntos del circuito.

Los resultados despus de haber armado el circuito y haber tomado las medidas respectivamente en el laboratorio se muestran en la siguiente tabla.MAGNITUD

VALOR MEDIDO

VALOR CALCULADO

VDS6.0V6.28V

VGS-0.67V-0.7V

VGD6.82V6.95V

IS2.02mA2.1mA

ID2.06mA2.1mA

IG0mA0mA

Clculos de los valores tericos

SABEMOS QUE:

Cuando

Estos dos datos nos permiten graficar y mediante la superposicin de grficas se obtienen los siguientes datos:

Conocemos que

Conclusiones: El valor del voltaje de estrangulamiento es el negativo del voltaje drenaje fuente (Vds), que hace que nuestra corriente de drenaje no vari mucho, mantenindose casi constante, esta corriente se llama corriente de saturacin. El voltaje de estrangulamiento es tambin igual al voltaje compuerta fuente (Vgs), en el cual nuestra corriente de drenaje se reduce a cero amperes.