515cachetgt4

-

Upload

tomi-sebastian-juarez -

Category

Documents

-

view

213 -

download

0

description

Transcript of 515cachetgt4

-

Practica 8 - PerformanceOrganizacion del Computador I

Veronica Coy

Departamento de Computacion - FCEyNUBA

2do Cuatrimestre de 2015

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Jerarqua de Memoria

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Hablemos sobre la memoria Cache... (1)

Que es una memoria Cache?

Es un espacio de almacenamiento intermedio entre el CPU y la memoria principal.

Por que la necesitamos?

Porque el crecimiento de la velocidad de los CPUs en las ultimas decadas ha sidoexponencial respecto al de las memorias. El uso de la cache sirve para minimizar eltiempo de acceso a los datos mejorando as la performance del sistema.

Cuanto mas rapida es?

Entre 10 y 100 veces mas rapida que la memoria principal.

Por que entonces no usamos solo memoria cache?

Porque la memoria cache es muy cara.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Hablemos sobre la memoria Cache... (2)

El problema

1. El CPU es muuuuy rapido.

2. La memoria rapida es cara y consume mucha energa.

3. La memoria barata y de bajo consumo es lenta.

4. Quiero tener mucha memoria, muy rapida, barata y queconsuma poca energa.

Una solucion

1. Uso mucha memoria de la barata y lenta,

2. y un poquito de memoria de la cara y rapida,

3. en la que mantengo una copia de los datos mas usados.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

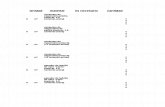

Registro L1 L2 L3 RAM0

20

40

60

80

100

120

Tiempo de Acceso (ns)

Registro L1 L2 L3 RAM0

500

1000

1500

2000

2500

Cantidad de memoria (KB)

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Como funciona?

Los pedidos a la cache se clasifican como:

I Hit: Si el dato de la direccion solicitada por el CPU se encuentra en cache.I Miss: En caso contrario.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Como medimos la performance?

En base a estos dos eventos, miss y hit, se obtienen metricas paraestimar el desempeno de una cache:

Hit Rate = cantidad de hitscantidad de pedidos

Miss Rate = cantidad de misscantidad de pedidos

Observacion:

Hit Rate + Miss Rate = 1

Nuestro objetivo es lograr que el hit rate sea lo mas alto posible.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Disenando una cache

Que cosas debera tener en cuenta a la hora de disenar una cache?

I Tamano: Debera ser lo suficientemente grande como paramaximizar los hits, pero a la vez, que sea lo suficientementepequena como para no afectar el nivel de consumo.

I Organizacion: Establecer de que forma vinculo las direccionesde memoria con las posiciones de mi cache.

I Poltica de desalojo: Que hacer cuando se llena la cache.I RandomI FIFO (First In First Out)I LFU (Least Frequently Used)I LRU (Least Recently Used)I . . .

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Estructura de una Cache

los niveles de cach. Como se observa en el grfico, si el tiempo para acceder a un registro es de un ciclo de reloj, un acceso a memoria RAM tiene un costo inmenso y el tiempo de espera requerido por esta operacin no puede ser utilizado para hacer cmputos: es un desperdicio importante de potencia computacional.

Las cachs funcionan por lo general bajo la hiptesis de localidad de referencia de varios tipos, en particular:

localidad espacial: si se utiliza un dato en memoria en un instante dado, es muy probable que en los instantes siguientes se utilice algn dato en una direccin cercana

localidad temporal: si se utiliza un dato en memoria en un instante dado, es muy probable que en los instantes siguientes se vuelva a utilizar

Caractersticas

La caracterstica primordial de una memoria cach es su funcin de mapeo. Esta funcin establece una o varias posiciones de cach en las que puede almacenarse una copia de una posicin de RAM dada. Dado que el tamao de la cach es siempre muy inferior al de la RAM, dicha funcin nunca puede ser inyectiva: necesariamente varias posiciones de la RAM sern almacenadas en la misma posicin de la cach (aunque no simultneamente!).

Por esta razn, ser necesario que al almacenar un dato en cach, se etiquete la posicin de la cach indicando el origen (la posicin en RAM) correspondiente al dato en cuestin. Esta etiqueta se denomina tag, y permite identificar cual de las mltiples posiciones de memoria que van a parar a una lnea dada de la cach se encuentra all en un momento determinado.

Las memorias cach se organizan y operan (cargan y descargan) en lneas, a diferencia de una memoria convencional que se opera de a palabras. A su vez, dentro de cada lnea, cada unidad direccionable tiene un ndice dentro de la misma.

Palabras por lnea

Lneas

Tags

ndices

0 1 2 3

I Lnea: Las memorias cache se componen por unidades denominadas lneas cuyotamano es multiplo del tamano de palabra que utiliza el CPU. Es la unidad quese carga cada vez que se hace un acceso a memoria.

I Indice: Un ndice permite ubicar una palabra dentro de una lneaI Tag: Es el identificador usado para mantener la correspondencia entre la lnea

en cache y la ubicacion de dicho contenido en memoria. El modo de trazar lacorrespondencia vara segun el tipo de cache.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache Totalmente Asociativa

Memoria

0x0 0x1 0x2 0x30x0 0xA 0x0 0x00x4 0x5 0x6 0x70x0 0x0 0xF 0x00x8 0x9 0xA 0xB0x0 0x0 0x5 0x00xC 0xD 0xE 0xF0x0 0x0 0x0 0x0

Cache

indicetag

00 01 10 11

Permite que cada lnea de memo-ria principal pueda cargarse encualquier lnea de la cache.

Cada una de estas lneas identifi-ca unvocamente una lnea de lamemoria principal por medio deltag o etiqueta.

Para decidir si una lnea esta en lacache se debe examinar todas lostags almacenados en la cache.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache Totalmente Asociativa

Memoria

0000 0001 0010 0011B.0

0000 1010 0000 00000100 0101 0110 0111

B.10000 0000 1111 00001000 1001 1010 1011

B.20000 0000 0101 00001100 1101 1110 1111

B.30000 0000 0000 0000

Cache

indicetag

00 01 10 11

Como se hace la asociacion entrelas posiciones de memoria y la lneade cache?

Dividiendo la memoria en lneas ynumerandolas:

#bloquesmem =|memoria||lineacache |

= |memoria||cache|#lineascache

= 16unidades

8unidades/bloque2

= 4 bloques 2 bits para tags

Cada bloque de memoria se va acorresponder con cualquier lnea decache.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache Totalmente Asociativa

Memoria

0000 0001 0010 0011B.0

0000 1010 0000 00000100 0101 0110 0111

B.10000 0000 1111 00001000 1001 1010 1011

B.20000 0000 0101 00001100 1101 1110 1111

B.30000 0000 0000 0000

Cache

indicetag

00 01 10 11

01 0000 0000 1111 0000

Pregunta:

Que ocurre cuando el CPU solicitala direccion 0x6?

Respuesta:

Tomo los dos primeros bits de ladireccion para identificar el tag:

0x6 01tag

10indice

Como el tag no esta cargado en

cache se produce un miss. Voya la memora, busco la lnea y latraigo.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache Totalmente Asociativa

Memoria

0000 0001 0010 0011B.0

0000 1010 0000 00000100 0101 0110 0111

B.10000 0000 1111 00001000 1001 1010 1011

B.20000 0000 0101 00001100 1101 1110 1111

B.30000 0000 0000 0000

Cache

indicetag

00 01 10 11

01 0000 0000 1111 0000

00 0000 1010 0000 0000

Pregunta:

Y si ahora quiere traer la direccion0x1?

Respuesta:

Idem:

0x1 00tag

01indice

Como el tag no esta cargado en

cache se produce un miss. Voya la memora, busco la lnea y latraigo.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache Totalmente Asociativa

Memoria

0000 0001 0010 0011B.0

0000 1010 0000 00000100 0101 0110 0111

B.10000 0000 1111 00001000 1001 1010 1011

B.20000 0000 0101 00001100 1101 1110 1111

B.30000 0000 0000 0000

Cache

indicetag

00 01 10 11

10 0000 0000 0101 0000

00 0000 1010 0000 0000

Pregunta:

Ahora, que ocurrira si el CPU pi-diera la direccion 0xA?:

Respuesta:

0xA 10tag

10indice

Miss de nuevo, pero ahora ten-go la cache llena. Debera desalojaralguna lnea, pero cual?

I RandomI FIFO (First In First Out)I LFU (Least Frequently

Used)

I LRU (Least Recently Used)

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache de Correspondencia Directa(o Mapeo Directo)

Memoria

0x0 0x1 0x2 0x30x0 0xA 0x0 0x00x4 0x5 0x6 0x70x0 0x0 0xF 0x00x8 0x9 0xA 0xB0x0 0x0 0x0 0x00xC 0xD 0xE 0xF0x0 0x5 0x0 0x0

Cache

indicetag

00 01 10 11

Lnea 0

Lnea 1

Consiste en partir la memoria prin-cipal en bloques del tamano dela cache. Luego, cada lnea delbloque tiene su lugar especfico enla cache.

Por cada lnea tengo que guardar aque bloque pertenece.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache de Correspondencia Directa(o Mapeo Directo)

Memoria

0000 0001 0010 00110000 1010 0000 00000100 0101 0110 0111

Blo

qu

e0

0000 0000 1111 00001000 1001 1010 10110000 0000 0000 00001100 1101 1110 1111

Blo

qu

e1

0000 0101 0000 0000

Cache

indicetag

00 01 10 11

Lnea 0

Lnea 1

Como se hace la asociacion entrelas posiciones de memoria y la lneade cache?

Dividiendo la memoria en bloquesy numerandolos:

#bloquesmem =|memoria||cache|

= 16unidades

8unidades/bloque

= 2 bloques 1 bit para tags

Cada bloque de memoria se va acorresponder lnea a lnea con elbloque entero de cache.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache de Correspondencia Directa(o Mapeo Directo)

Memoria

0000 0001 0010 00110000 1010 0000 00000100 0101 0110 0111

Blo

qu

e0

0000 0000 1111 00001000 1001 1010 10110000 0000 0000 00001100 1101 1110 1111

Blo

qu

e1

0000 0101 0000 0000

Cache

indicetag

00 01 10 11

Lnea 0

0 0000 0000 1111 0000 Lnea 1

Pregunta:

Que ocurre cuando el CPU solicitala direccion 0x6?

Respuesta:

Tomo el primer bit de la direccionpara identificar el tag y el siguientepara identificar la lnea:

0x6 0tag

1lnea

10ndice

Como el tag no esta cargado en

cache se produce un miss. Pidoa memoria toda la lnea.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache de Correspondencia Directa(o Mapeo Directo)

Memoria

0000 0001 0010 00110000 1010 0000 00000100 0101 0110 0111

Blo

qu

e0

0000 0000 1111 00001000 1001 1010 10110000 0000 0000 00001100 1101 1110 1111

Blo

qu

e1

0000 0101 0000 0000

Cache

indicetag

00 01 10 11

0 0000 1010 0000 0000 Lnea 0

0 0000 0000 1111 0000 Lnea 1

Pregunta:

Y si ahora pide la direccion 0x1?

Respuesta:

Idem:

0x1 0tag

0lnea

01ndice

Como el tag ya esta cargado enmemoria, pero la lnea 0 no, se pro-

duce un miss. Pido a memoriatoda la lnea.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache de Correspondencia Directa(o Mapeo Directo)

Memoria

0000 0001 0010 00110000 1010 0000 00000100 0101 0110 0111

Blo

qu

e0

0000 0000 1111 00001000 1001 1010 10110000 0000 0000 00001100 1101 1110 1111

Blo

qu

e1

0000 0101 0000 0000

Cache

indicetag

00 01 10 11

0 0000 1010 0000 0000 Lnea 0

1 0000 0101 0000 0000 Lnea 1

Pregunta:

Ahora, que ocurrira si el CPU pi-diera la direccion 0xD?

Respuesta:

0xD 1tag

1lnea

01ndice

Como el tag no esta cargado

en cache, se produce un missporque se que esa lnea no esta encache.

Pero ahora, como micache esta llena, voy a tenerque reemplazar la lnea correspon-diente en cache.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache Asociativa por Conjuntos de N Vas

Memoria

0x0 0x10x0 0xD0x2 0x30xA 0x00x4 0x50x0 0x00x6 0x70x0 0x80x8 0x90x0 0x00xA 0xB0x0 0xE

Cache

tag 0 1 tag 0 1

Set 0 Set 1

via 1

via 0

Es un tipo de cache que combinacaractersticas de los dos tipos decache que vimos previamente.

Es muy similar a la Cache deCorrespondencia Directa, pero conel agregado de vas que permitenpersistir las lneas de memoria encache por mas tiempo.

Vamos a ver un ejemplo de 2 vas,es extensible a N vas

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache Asociativa por Conjuntos de N Vas

Memoria

0000 00010000 11010010 0011

Blo

qu

e0

1010 00000100 01010000 00000110 0111

Blo

qu

e1

0000 10001000 10010000 00001010 1011

Blo

qu

e2

0000 1110

Cache

tag 0 1 tag 0 1

Set 0 Set 1

via 1

via 0

Como se hace la asociacion entrelas posiciones de memoria y la lneade cache?

Dividiendo la memoria en bloquesy numerandolos:

#bloques =mem|memoria||via|

= |memoria||cache|#vias

= 12unidades

8unidades/bloque2

= 3 bloques 2 bits para tags

Cada bloque de memoria se va acorresponder lnea a lnea con laslneas de cada va de la cache.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache Asociativa por Conjuntos de N Vas

Memoria

0000 00010000 11010010 0011

Blo

qu

e0

1010 00000100 01010000 00000110 0111

Blo

qu

e1

0000 10001000 10010000 00001010 1011

Blo

qu

e2

0000 1110

Cache

tag 0 1 tag 0 1

Set 0 00 1010 0000 Set 1

via 1

via 0

Pregunta:

Que ocurre cuando el CPU solicitala direccion 0x2?

Respuesta:

Tomo los dos primeros bits de ladireccion para identificar el tag y elsiguiente para identificar el set:

0x2 00tag

1set

0ndice

Como el tag no esta cargado encache se produce un miss. Pido amemoria la lnea entera.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache Asociativa por Conjuntos de N Vas

Memoria

0000 00010000 11010010 0011

Blo

qu

e0

1010 00000100 01010000 00000110 0111

Blo

qu

e1

0000 10001000 10010000 00001010 1011

Blo

qu

e2

0000 1110

Cache

tag 0 1 tag 0 1

00 0000 1101 Set 0 00 1010 0000 Set 1

via 1

via 0

Pregunta:

Y si ahora pide la direccion 0x1?

Respuesta:

Idem:

0x1 00tag

0set

1ndice

Como la lnea no esta cargada encache se produce un miss. Pido amemoria la lnea entera.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache Asociativa por Conjuntos de N Vas

Memoria

0000 00010000 11010010 0011

Blo

qu

e0

1010 00000100 01010000 00000110 0111

Blo

qu

e1

0000 10001000 10010000 00001010 1011

Blo

qu

e2

0000 1110

Cache

tag 0 1 tag 0 1

00 0000 1101 Set 010 0000 1110 00 1010 0000 Set 1

via 1

via 0

Pregunta:

Ahora, que ocurrira si el CPU pi-diera la direccion 0xB?

Respuesta:

0xB 10tag

1set

1ndice

Como el tag no esta cargado encache, se produce un miss.

La direccion pedida corresponde alset 1 y como tengo espacio puedotraerla.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache Asociativa por Conjuntos de N Vas

Memoria

0000 00010000 11010010 0011

Blo

qu

e0

1010 00000100 01010000 00000110 0111

Blo

qu

e1

0000 10001000 10010000 00001010 1011

Blo

qu

e2

0000 1110

Cache

tag 0 1 tag 0 1

00 0000 1101 Set 010 0000 1110 00 1010 0000 Set 1

via 1

via 0

Cuando el CPU solicita nueva-mente la direccion 0x2:

Tomo los dos primeros bits de ladireccion para identificar el tag y elsiguiente para identificar el set:

0x2 00tag

1set

0ndice

Como el tag esta cargado encache se produce un hit.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Cache Asociativa por Conjuntos de N Vas

Memoria

0000 00010000 11010010 0011

Blo

qu

e0

1010 00000100 01010000 00000110 0111

Blo

qu

e1

0000 10001000 10010000 00001010 1011

Blo

qu

e2

0000 1110

Cache

tag 0 1 tag 0 1

00 0000 1101 Set 001 0000 1000 00 1010 0000 Set 1

via 1

via 0

Pregunta:

Y si despues el CPU pide la direc-cion 0x7?

Respuesta:

0x7 01tag

1set

1ndice

Como el tag no esta cargado encache, se produce un miss.

De nuevo, la direccion pedida cor-responde al set 1. Sin embargo, yatengo todas las vas de mi set com-pletas. Que hago?

Desalojo la lnea de alguna de lasvas del set 1 usando alguna delas polticas que vimos antes. Porejemplo: LFU.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Ejercicio 1 - Correspondencia directa

Memoria Principal: 220 bytes, direccionable a byte.Cache: 32 lneas de 16 bytes cada una.

Responder:

1. Cuanto mide un bloque para esta configuracion?

2. Cuantos bloques entran en memoria principal?

3. Cuantas lneas entran en un bloque?

4. Como puedo saber si esta cargada la lnea donde seencuentra la palabra referida por la direccion C34A6?

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

1. Cuanto mide un bloque para esta configuracion? Para estaconfiguracion, coincide con el tamano de la cache

# lneas cache x capacidad de una lnea = 32lneax16B

lnea= 512B = 29B

2. Cuantos bloques entran en memoria principal?

capacidad memoria

tamano bloque=

220B

29B/bloque= 211bloque

3. Cuantas lneas entran en un bloque? Para esta configuracion, tantascomo entren en la cache:

capacidad cache

capacidad de una lnea=

512B

16B/lnea=

29B

24B/lnea= 25 lnea

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

4. Como puedo saber si esta cargada la lnea donde seencuentra la palabra referida por la direccion C34A6?Primero me fijo cuanto mide cada campo de una direccion de memoria para esta

configuracion de cache: tag 11 bits, lnea 5 bits, ndice 4 bits. Despues, paso la

direccion a binario para saber el valor de los campos correspondientes a esa

direccion.I La direccion en binario:

C

1100

3

0011

4

0100

A

1010

6

0110

I Agrupada segun los campos tag, lnea e ndice:

61A

110 0001 1010

A

0 1010

6

0110

Finalmente, me tengo que fijar si en el lugar reservado para las lneas numero

0xA, esta cargada la lnea correspondiente al bloque numero 0x61A; si es as, la

lnea correspondiente a la direccion pedida esta cargada en cache.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Ejercicio 2 - Asociativa por conjuntos

Memoria Principal: 1 MB, direccionable a byte.Cache: 32 lneas de 64 bytes cada una, 2 vas.

Responder:

1. Cuanto mide un bloque para esta configuracion?

2. Cuantos bloques entran en memoria principal?

3. Cuantas lneas entran en un bloque?

4. Como puedo saber si esta cargada la lnea donde seencuentra la palabra referida por la direccion C34A6?

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

1. Cuanto mide un bloque para esta configuracion? Para estaconfiguracion, coincide con el tamano de una va

# lneas por va =# lneas cache

# vas=

32 lneascache

2 vascache

= 16lneas

va= 24

lneas

va

# lneas por va x capacidad de una lnea = 24lneas

vax 64

B

lnea= 210

B

va

2. Cuantos bloques entran en memoria principal?

capacidad memoria

tamano bloque=

1MB

210B/bloque=

220B

210B/bloque= 210bloque

3. Cuantas lneas entran en un bloque? Para esta configuracion, tantascomo entren en una va: 24 (ver punto 1).

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

4. Como puedo saber si esta cargada la lnea donde seencuentra la palabra referida por la direccion C34A6?Primero me fijo cuanto mide cada campo de una direccion de memoria para estaconfiguracion de cache: tag 10 bits, conjunto 4 bits, ndice 6 bits. Despues,paso la direccion a binario para saber el valor de los campos correspondientes aesa direccion.

I La direccion en binario:

C

1100

3

0011

4

0100

A

1010

6

0110

I Agrupada segun los campos tag, conjunto e ndice:

30D

11 0000 1101

2

0010

26

10 0110

Finalmente, me tengo que fijar si en el lugar reservado para las lneas numero

0x2, esta cargada la lnea correspondiente al bloque numero 0x30D, en

cualquiera de los dos espacios del conjunto; si es as, la lnea correspondiente a

la direccion pedida esta cargada en cache.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Ejercicio 3 - Ejercicio de parcial

Se estudia agregar una memoria cache a una computadora cuyaspalabras y direcciones de memoria son de 16 bits, y que trabajacon direccionamiento a byte.Hasta el momento se barajan dos opciones:

I Una cache asociativa por conjuntos de 4 vas

I Una de correspondencia directa (o mapeo directo), utilizandoFIFO como poltica de desalojo

Cada cache puede almacenar hasta 1024 bytes de informacion (sincontar el espacio necesario para los tags) y se organiza en 64 lneasen total.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

a) Indique como se distribuyen los bits de una direccion de memoria en los camposcorrespondientes para cada una de las caches mencionadas.

b) Se conoce que este fragmentode codigo insume gran partedel tiempo de computo.Junto a cada instruccion seindica el acceso a memorianecesario para el fetch de lainstruccion, no as los necesar-ios para acceder a los datos.

Codigo Pedido a memoriadel fetch

MOV R6, 0x10 0x9C13MOV R2, 0x801A 0x9C15, 0x9C17

mejillon: ADD R5, [R2] 0x9C19ADD R5, [R2 + 0x15] 0x9C1BSUB R6, 0x01 0x9C1DCMP R6, 0x00 0x9C1FJNE mejillon 0x9C21

Simule los accesos a memoria que realiza este programa hasta la comparacion(inclusive) utilizando la cache de mapeo directo. Tenga en cuenta los accesos adatos, que no fueron detallados en la tabla. Indique en cada paso el contenido dela cache, y cuando corresponda detalle si se producen hits, misses, desalojos(senalando la lnea desalojada) y/o accesos desalineados. Cual es el hit rate deesta ejecucion parcial?

c) Cual de las dos caches es mas conveniente para la ejecucion completa delfragmento del programa presentado?

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

a) Correspondencia directa

1. Cuanto mide un bloque para esta configuracion?Para esta configuracion,coincide con el tamano de la cache, es decir 210 B (lo dice el enunciado)

2. Cuantos bloques entran en memoria principal?

capacidad memoria

tamano bloque=

# direcciones x tamano unidad dir.

tamano bloque=

216x1B

210B= 26

3. Cuantas lneas entran en un bloque?Para esta configuracion, tantas comoentren en la cache:

capacidad de una lnea =capacidad cache

# lneas en cache=

210B

64=

210B

26= 24B

capacidad cache

capacidad de una lnea=

210B/cache

24B/linea= 26

linea

cache

4. Cuantas direcciones distintas refieren a una misma lnea?

tamano del tag x tamano de la linea = 26 bits x 24 bits = 210direcciones

Por lo tanto, la decodificacion de la direccion de 16 bits sera

tag lnea ndice6 bits 6 bits 4 bits

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

(a) Asociativa por conjuntos1. Cuanto mide un bloque para esta configuracion?

Para esta configuracion, coincide con el tamano de una va.

capacidad cache

# vas=

210B

4= 28B

2. Cuantos bloques entran en memoria principal?

capacidad memoria

tamano bloque=

# direcciones x tamano unidad dir.

tamano bloque=

216x1B

28B= 28

3. Cuantas lneas entran en un bloque?Hay 64 lneas, que se dividen entre las 4 vas. Por lo tanto, hay 64

4= 16 = 24

conjuntos.

4. Cuantas direcciones distintas refieren a una misma lnea?

tamano del tag x tamano de la linea = 28 bits x 24 bits = 212direcciones

Por lo tanto, la codificacion sera

tag conjunto ndice8 bits 4 bits 4 bits

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

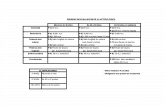

(b) Accesos a memoria - Acceso directoDireccion Tag Lnea Indice Resultado Estado Cache Notas

0x9C13 27 1 3 Miss {1: 27} cargue 1:2727

10 011101

00 00013

00110x9C15 27 1 5 Hit {1: 27}

2710 0111

0100 0001

50101

0x9C17 27 1 7 Hit {1: 27}27

10 011101

00 00017

01110x9C19 27 1 9 Hit {1: 27}

2710 0111

0100 0001

91001

0x801A 20 1 A Miss {1: 20} desaloje 1: 27;20

10 000001

00 0001A

1010cargue 1:20

0x9C1B 27 1 B Miss {1: 27} desaloje 1: 20;27

10 011101

00 0001B

1011cargue 1:27

0x802F 20 2 F Miss {1: 27} acc. desalineado;20

10 000002

00 0010F

1111{2: 20} cargue 2: 20;{3: 20} cargue 3: 20

0x9C1D 27 1 D Hit27

10 011101

00 0001D

11010x9C1F 27 1 F Miss {1: 27} acc. desalineado;

2710 0111

0100 0001

F1111

{2: 27} desaloje 2:20;{3: 20} cargue 2: 27

Hit rate = 49 0.44 %

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

(c) Comparacion - TareaIdea de solucion:

Para este bloque de codigo sera mas conveniente la cache asociativa por conjuntos de

4 vas, ya que se eliminaran los desalojos gracias al mas alto nivel de asociatividad.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Acceso Desalineado

Un acceso desalineado es una situacion especial que se da cuandose realiza un acceso a memoria en una posicion cuya palabrasobrepasa el lmite de la lnea de cache. En este caso, parasatisfacer el ultimo pedido de lectura desde cache, sera necesariocargar dos lneas de cache en vez de una.

Un acceso desalineado es considerado un Hit sii ambas lneas yaestan en la cache. Si falta una o las dos es considerado un unicoMiss.

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Por que funciona la cache (localidad espacial)

i n t a r r e g l o [ 1 0 0 0 0 ] = {/ . . . / } ;i n t c o n t a d o r = 0 ;

f o r ( i n t i = 0 ; i < 10000 ; i++){

i f ( a r r e g l o [ i ] > 4)c o n t a d o r++;

}

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Por que funciona la cache (localidad temporal)

i n t a r r e g l o [ 1 0 0 0 0 ] = {/ . . . / } ;i n t c o n t a d o r = 0 ;

f o r ( i n t i = 0 ; i < 10000 ; i ++){

i f ( a r r e g l o [ i ] > 4)c o n t a d o r++;

}

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

-

Preguntas?

Organizacion del Computador I Practica 8 - Performance 2do Cuatrimestre de 2015

IntroduccinOrganizacin de la CachCach Totalmente AsociativaCach de Correspondencia DirectaCach Asociativa por Conjuntos de N Vas

EjerciciosEjercicio 1 - Correspondencia directaEjercicio 2 - Asociativa por conjuntosEjercicio 3 - Ejercicio de parcialFin