Universidad Técnica Federico Santa María Departamento de ...ramos.elo.utfsm.cl/~elo312/msp/Memoria...

Transcript of Universidad Técnica Federico Santa María Departamento de ...ramos.elo.utfsm.cl/~elo312/msp/Memoria...

Universidad Técnica Federico Santa María

Departamento de Electrónica

Técnicas de Diseño con Microcontrolador

MSP430

Memoria presentada por Jaime A. Zúñiga Camiruaga

Para optar al título de

Ingeniero Civil Electrónico

Mención Computadores

Profesor Guía: Sr. Leopoldo Silva B.

Diciembre de 2003

ii

Resumen

En el trabajo se realiza una introducción a la familia de microcontroladores MSP430 de Texas Instruments, analizando sus características más avanzadas y su interconexión con diversos periféricos disponibles en la tarjeta de desarrollo EasyWeb de Olimex, tales como memoria eeprom serial, módulo de cristal líquido alfanumérico, puerto serial RS232, y controlador ethernet.

El trabajo está orientado a los sistemas digitales y principalmente a la programación de microcontroladores. Se da una visión práctica del diseño con microcontroladores, para lo cual si bien existe abundante documentación disponible, ésta se encuentra dispersa y en algunos casos es demasiado extensa. Esto representa un problema cuando no se tiene demasiado tiempo para comenzar a trabajar. Por ello es de gran ayuda contar con una guía que sirva de introducción al tema del diseño con microcontrolador. Para concretar esta guía se trabajó en laboratorio con la tarjeta de desarrollo apoyado por los manuales y hojas de características de cada componente en particular, así como búsqueda de información en Internet.

iii

Índice de contenido

Resumen............................................................................................... ii

Índice de contenido ............................................................................. iii

Índice de figuras ................................................................................... v

Índice de tablas .................................................................................. vii

Prefacio ............................................................................................. viii

Introducción........................................................................................ ix

Capítulo 1 El microcontrolador MSP430 ............................................... 1

1.1 Introducción....................................................................................... 1

1.2 Mapa de memoria e interrupciones ..................................................... 2

1.3 Los puertos de entrada y salida digital ................................................ 4

1.4 El módulo de reloj............................................................................... 6

1.5 El multiplicador por hardware ............................................................ 8

1.6 Modos de bajo consumo...................................................................... 9

1.7 Los temporizadores............................................................................. 9

1.7.1 El temporizador watchdog ............................................................ 9

1.7.2 Los Temporizadores A y B........................................................... 10

1.7.3 El comparador analógico y los conversores análogo a digital ....... 14

Capítulo 2 La tarjeta de desarrollo EasyWeb II .................................... 19

2.1 Descripción del circuito .................................................................... 19

iv

Capítulo 3 Introducción a protocolos de comunicación entre dispositivos ........................................................................................ 29

3.1 El protocolo I²C y la memoria EEPROM serial 24LC515..................... 30

3.2 Los dispositivos iButton de Dallas Semiconductors y el protocolo propietario 1-Wire................................................................................... 36

3.3 Control de un módulo de cristal líquido alfanumérico ....................... 42

3.4 Utilización del protocolo TCP/IP en sistemas embebidos ................... 47

3.4.1 El hardware para sistemas embebidos con conexión ethernet ..... 47

3.4.2 El software del microcontrolador................................................. 51

Conclusiones ...................................................................................... 59

Referencias......................................................................................... 60

Anexo ................................................................................................. 62

v

Índice de figuras

Figura 1-1 Designación de patillas del microcontrolador .............................. 5

Figura 1-2 Módulo de reloj........................................................................... 7

Figura 1-3 Diagrama del multiplicador por hardware ................................... 8

Figura 1-4 Modos del temporizador A como temporizador/contador. ......... 11

Figura 1-5 Modos del temporizador B como temporizador/contador.......... 12

Figura 1-6 Salidas del temporizador A en modo contador continuo ........... 13

Figura 1-7 Efecto del filtro pasabajos en la salida ..................................... 14

Figura 1-8 Diagrama del comparador analógico ........................................ 15

Figura 1-9 Diagrama del conversor análogo a digital ................................. 16

Figura 1-10 Tiempos de muestreo y conversión......................................... 17

Figura 2-1 Tarjeta de desarrollo ................................................................ 19

Figura 2-2 Esquema de conexiones del microcontrolador .......................... 20

Figura 2-3 Diagrama de fuente de alimentación ........................................ 21

Figura 2-4 Conexión de pulsadores........................................................... 22

Figura 2-5 Esquema de optoacoplador ...................................................... 22

Figura 2-6 Conexión de optoacopladores................................................... 23

Figura 2-7 Conexión de relés .................................................................... 23

Figura 2-8 Conexión a la memoria Flash................................................... 24

Figura 2-9 Conexión del display de cristal líquido ..................................... 24

Figura 2-10 Conexión del puerto serial ..................................................... 25

Figura 2-11 Conexiones de cable serial ..................................................... 25

Figura 2-12 Esquema de conectores ......................................................... 26

Figura 2-13 Conexión del controlador ethernet ......................................... 27

vi

Figura 2-14 Programador y emulador ....................................................... 28

Figura 2-15 Esquemático del programador ............................................... 28

Figura 3-1 Comunicación I²C.................................................................... 31

Figura 3-2 Byte de control ........................................................................ 32

Figura 3-3 Direccionamiento de la memoria.............................................. 32

Figura 3-4 Escritura de un byte................................................................ 33

Figura 3-5 Escritura de una página de hasta 64 bytes .............................. 33

Figura 3-6 Diagrama de flujo de fin de escritura ....................................... 34

Figura 3-7 Lectura de posición aleatoria ................................................... 35

Figura 3-8 Lectura de posiciones sucesivas............................................... 35

Figura 3-9 Lectura de dirección actual...................................................... 35

Figura 3-10 Esquema eléctrico de iButton ................................................ 36

Figura 3-11 Apariencia de un dispositivo iButton...................................... 37

Figura 3-12 Pulso de reset y presencia...................................................... 38

Figura 3-13 Escritura en dispositivos iButton........................................... 38

Figura 3-14 Lectura desde dispositivos iButton......................................... 39

Figura 3-15 Generación de reset y estado de dispositivo............................ 39

Figura 3-16 Lectura de un bit desde dispositivo iButton ........................... 40

Figura 3-17 Escritura de un bit en dispositivo iButton.............................. 40

Figura 3-18 Modelo ISO/OSI versus modelo Internet ................................ 47

Figura 3-19 Diagrama esquemático del CS8900A...................................... 49

Figura 3-20 Interconexión microcontrolador a controlador ethernet .......... 49

Figura 3-21 Captura de paquetes arp y echo............................................. 53

Figura 3-22 Transacción http ................................................................... 54

Figura 3-23 Diagrama de programa de usuario usando DoNetworkStuff() . 57

vii

Índice de tablas

Tabla 1-1 Mapa de memoria del MPS430 ..................................................... 2

Tabla 1-2 Vector de interrupciones .............................................................. 4

Tabla 1-3 Modos del contador.................................................................... 11

Tabla 1-4 Modos de operación del conversor análogo a digital .................... 17

Tabla 3-1 Función de pines del módulo de cristal líquido ........................... 42

Tabla 3-2 Comandos del módulo de cristal líquido ..................................... 43

Tabla 3-3 Caracteres disponibles en el módulo de cristal líquido ................ 46

viii

Prefacio

El presente trabajo se encuentra estructurado en tres capítulos que introducen los conceptos básicos sobre el trabajo con el microcontrolador MSP430 y la utilización de los periféricos disponibles en la tarjeta de desarrollo Easyweb.

El primer capítulo proporciona una visión general sobre los distintos componentes del microcontrolador y de sus diversas capacidades.

El segundo capítulo trata sobre el diseño de la tarjeta de desarrollo a utilizar, describiendo el circuito y justificando la elección de los componentes que lo constituyen. En este capítulo sólo se tratan aspectos de hardware por lo que es casi independiente del primer capítulo.

El tercer capítulo contiene múltiples referencias a los dos capítulos anteriores por lo que se recomienda su lectura posterior a los dos primeros. En él se describen técnicas de comunicación entre periféricos, básicamente los disponibles en la tarjeta de desarrollo, se describe tanto los requerimientos de hardware como de software para su interconexión.

ix

Introducción

Al diseñar sistemas basados en un microcontrolador habitualmente es necesario interconectar diversos componentes, por lo que es necesario conocer las técnicas utilizadas, los protocolos y estándares utilizados por los distintos fabricantes y por las instituciones que rigen a la industria. Además el conocer distintas técnicas le da al diseñador herramientas adicionales al momento de definir su estrategia o enfrentarse con nuevos procedimientos que aparezcan en el futuro, o que pertenezcan al área de trabajo en que se desarrolla.

La variedad de protocolos y técnicas de comunicación entre periféricos se pueden dividir entre seriales y paralelos, a su vez los seriales se dividen en sincrónicos y asincrónicos. La diferencia entre éstos radica en la presencia o no de una señal de reloj en las líneas de comunicación. En el ámbito de la comunicación entre circuitos integrados dentro de la misma placa de circuito impreso o a muy corta distancia, algunos centímetros o metros, la mayor cantidad de protocolos que se encuentran son seriales debido a la poca cantidad de líneas de comunicación que se requieren.

De igual forma es necesario que el diseñador conozca las últimas técnicas de trabajo con microcontroladores, como emuladores en línea, interfaces para señales analógicas, ahorro de energía en sistemas portátiles, y otros.

Un buen representante de los microcontroladores modernos es la familia de microcontroladores MSP430 de Texas Instruments. Estos microcontroladores de 16 bits son dispositivos de muy bajo consumo de energía (desde pocos µA hasta algunos mA), dependiendo del modo de bajo consumo que el diseñador elija, además cuentan con conversores análogo a digital y comparadores para señales analógicas. El trabajo con este microcontrolador se facilita por su capacidad de utilizar un emulador en línea con una interfaz JTAG, esto permite descargar código a su memoria Flash, leer y escribir el estado de la memoria RAM y sus registros, y ejecutar el código paso a paso desde una interfaz gráfica. El estándar JTAG de IEEE se encuentra presente en cada vez más dispositivos, por lo que resulta conveniente conocerlo. Otra ventaja de este microcontrolador es que debido a su amplia utilización existen variadas herramientas de software para trabajar con él, algunas incluso de libre distribución como el GNU C Compiler portado a la arquitectura.

A medida que se expande el uso de Internet y de las redes de computadores toma cada vez más fuerza la idea de tener dispositivos conectados a la red para controlarlos o monitorearlos en forma remota desde cualquier lugar con acceso a Internet. Algo que puede parecer algo oscuro y

x

complicado en un principio se logra comprender cuando se trabaja con los protocolos involucrados, al mismo tiempo se logra experiencia en un campo de rápido crecimiento. El hardware utilizado para ello es bastante simple si se utiliza un microcontrolador moderno. Después que el diseñador ha comprobado sus ideas, en un ambiente de desarrollo, puede implementar lo aprendido en sus futuros proyectos, ya que el costo que involucra conectar un dispositivo a la red es menor en comparación al resto del sistema, al mismo tiempo la capacidad de procesamiento del microcontrolador es suficiente para manejar la conexión de red y preocuparse de las otras tareas que requiera el sistema sin mayor penalización en el rendimiento.

Debido a que los circuitos integrados de cierta complejidad tienden a venir en encapsulados de montaje superficial se dificulta trabajar con ellos en etapas de prototipos. Por esta razón las tarjetas de desarrollo de propósito general proporcionan al diseñador una herramienta que ahorra un tiempo considerable a la hora de desarrollar un sistema microcontrolado. Una vez que el software se encuentra funcionando correctamente se puede proceder a la fabricación del hardware del prototipo para su depuración final. Una vez más en esta etapa del trabajo los nuevos microcontroladores que permiten programación y depuración una vez montados en el circuito final facilitan en gran medida la actualización o corrección del software, proporcionando una herramienta invaluable al programador.

1

Capítulo 1 El microcontrolador MSP430

1.1 Introducción

El MSP430 de Texas Instruments es un microcontrolador con un conjunto reducido de instrucciones (RISC) de 16 bits diseñado especialmente para aplicaciones que requieran un muy bajo consumo de energía, tales como dispositivos portátiles. Además mezcla señales analógicas y digitales en un solo circuito, lo que simplifica el diseño del hardware, y reduce el costo, debido a que no es necesario instalar conversores análogo a digital por separado. Por el hecho de trabajar con palabras de 16 bits es especialmente indicado para ser programado en lenguajes de alto nivel, por ejemplo C o C++ para sistemas embebidos, generando un código compacto y de rápida ejecución.

La principal fuente de información acerca de este dispositivo son: la guía del usuario del MSP430[1] y las hojas de datos del dispositivo en particular, en este caso del MSP430F149[2]. Su arquitectura corresponde a un modelo Von-Neumann en el que tanto la memoria RAM y ROM comparten un solo mapa de memoria de hasta 64KB. Posee un sistema de reloj particularmente flexible que posee 3 osciladores independientes, pensados para ahorrar energía. Además incorpora una serie de periféricos mapeados a memoria, tales como: 3 temporizadores, 8 canales de conversores análogo a digital, dos puertos seriales sincrónicos o asincrónicos de comunicación, un módulo de multiplicación por hardware, un comparador de niveles analógicos, un módulo controlador de memoria Flash que permite que el dispositivo se reprograme a si mismo, o guarde información en un espacio de memoria no volátil.

A continuación se detallarán los aspectos más relevantes de este microcontrolador, específicamente del dispositivo MSP430F149, ya que con él se realizará el trabajo posterior. En adelante se hará referencia a los nombres de los registros como figuran en los archivos de definiciones del compilador de C (ver anexo), todos los compiladores utilizan la misma definición entregada por Texas Instruments, de forma de obtener mayor compatibilidad entre ellos; en lugar de la dirección que ocupan en memoria. Cabe recordar que los registros de funciones especiales y generales son de 16 bits, y las direcciones de acceso a periféricos pueden ser de 8 ó 16 bits dependiendo del periférico en cuestión

2

1.2 Mapa de memoria e interrupciones

EL microcontrolador MSP430 cuenta con un direccionamiento de memoria de 16 bits por lo que se encuentra limitado a 64 KB de memoria total. El mapa se divide en RAM: registros de funciones especiales, acceso a periféricos de 8 bits, de 16 bits y 2 KB de memoria de uso general, ROM: memoria del cargador de software, y FLASH: memoria no volátil de información de usuario, 60 KB de memoria de código y el vector de interrupciones:

Tabla 1-1 Mapa de memoria del MPS430

Tipo de memoria Uso DirecciónFLASH Tamaño 60KB

Vector de interrupciones FFE0-FFFFCódigo 1100-FFFFMemoria de información Tamaño 256 bytes

1000-10FFROM Cargador de software Tamaño 1KB

0C00-0FFFRAM RAM de uso general Tamaño 2KB

0200-09FFPeriféricos 16 bits 0100-01FFPeriféricos 8 bits 0010-00FFRegistros especiales 0000-000F

La grabación en la memoria Flash se puede hacer por bits, bytes o palabras. La diferencia entre el sector de código y el sector de memoria de información es que el primero se puede borrar en bloques de 512 bytes, en tanto el segundo se puede borrar en bloques de 128 bytes (2 bloques en total), lo que lo hace más indicado para almacenar información de usuario, pero ello no impide que se pueda utilizar la sección de código no utilizada para almacenar información.

El cargador de software[3] es un programa precargado en el microcontrolador que permite descargar código a la memoria FLASH y/o RAM mediante una conexión serial. Para utilizarlo se indica a la CPU que se reinicie y comience la ejecución en la dirección de memoria correspondiente al cargador de software (Bootstrap Loader), esto se consigue aplicando una secuencia especial en los pines RESET y TEST. A continuación se utiliza el puerto serial para acceder a la memoria, ya sea para escribir o leer su

3

contenido. La forma sugerida por Texas Instruments para realizar la conexión al puerto serial de un computador es utilizar los pines DTR y RTS del puerto para manejar los pines RESET y TEST del microcontrolador y proporcionar la secuencia necesaria, mientras los pines RX y TX se utilizan para la comunicación. Por supuesto se deben conectar mediante un cambiador de niveles para adaptar la interfaz RS232 a los niveles de tensión que utiliza el microcontrolador. Los comandos están descritos en la literatura proporcionada por TEXAS[3].

Las interrupciones en el microcontrolador pueden ser de tres tipos, de reset, enmascarables y no enmascarables. La diferencia entre estas últimas es que las enmascarables se pueden habilitar o deshabilitar individualmente o mediante el flag de habilitación general de interrupciones, en tanto las no enmascarables sólo se pueden habilitar o deshabilitar individualmente, el flag de habilitación general no afecta su comportamiento. El vector de interrupciones del microcontrolador cuenta con 16 direcciones, algunas de las cuales tienen múltiples fuentes de interrupción, por ejemplo, cualquiera de los 8 bits de los puertos 1 ó 2 puede generar una interrupción, la rutina de atención de interrupciones debe verificar el estado de los 8 flags del registro de interrupciones del puerto para saber en cual pin se generó la condición de interrupción.

En la Tabla 1-2 se puede ver el vector de interrupciones del microcontrolador MSP430F149.

4

Tabla 1-2 Vector de interrupciones

Fuente de interupcion Flags afectado Tipo de interrupción Dirección PrioridadEncendido WDTIFG Reset 0FFFEh 15, mayor

Reset externo KEYVWatchdog

Memoria FlashNMI NMIIFG (No)enmascarable 0FFFCh 14

Falla del oscilador OFIFG (No)enmascarableViolación de acceso a Flash ACCVIFG (No)enmascarable

Timer_B7 TBCCR0 CCIFG Enmascarable 0FFFAh 13Timer_B7 TBCCR1 al 6 CCIFGs, Enmascarable 0FFF8h 12

TBIFGComparador_A CAIFG Enmascarable 0FFF6h 11Watchdog timer WDTIFG Enmascarable 0FFF4h 10

USART0 recepción URXIFG0 Enmascarable 0FFF2h 9USART0 transmisión UTXIFG0 Enmascarable 0FFF0h 8

ADC12 ADC12IFG Enmascarable 0FFEEh 7Timer_A3 TACCR0 CCIFG Enmascarable 0FFECh 6Timer_A3 TACCR1 CCIFG, Enmascarable 0FFEAh 5

TACCR2 CCIFG,TAIFG

I/O puerto 1 P1IFG.0 al P1IFG.7 Enmascarable 0FFE8h 4USART1 recepción URXIFG1 Enmascarable 0FFE6h 3

USART1 transmisión UTXIFG1 Enmascarable 0FFE4h 2I/O puerto 2 P2IFG.0 al P2IFG.7 Enmascarable 0FFE2h 1

0FFE0h 0, menor

1.3 Los puertos de entrada y salida digital

El microcontrolador MSP430F149 tiene 6 puertos de 8 bits de entrada y salida, cuyos terminales se encuentran multiplexados con otros periféricos como se puede ver en la Figura 1-1 [1].

5

Figura 1-1 Designación de patillas del microcontrolador

Cada bit del puerto se puede manejar en forma independiente. El control y acceso a los puertos se realiza mediante 4 registros por cada uno de los n puertos, los que almacenan los datos de entrada (PnIN), de salida (PnOUT), la dirección de entrada o salida (PnDIR) y la función como puerto de entrada y salida o como el periférico correspondiente (PnSEL). Cuando un bit se ocupa para controlar un periférico no se configura automáticamente como de entrada o salida, sino que es trabajo del programador seleccionar el sentido correcto.

Los dos primeros puertos tienen capacidad de generar interrupciones en cada uno de sus 8 bits. El registro de habilitación de interrupciones (PnIE) define que patilla del puerto genera interrupciones, el registro de selección de canto (PnIES) selecciona la transición que generará interrupciones (canto de bajada o de subida), y el registro que contiene los flags de interrupción (PnIFG) indica qué patilla generó la interrupción. Cada puerto lleva a un solo vector de interrupciones por lo que la rutina de atención de interrupciones debe verificar el estado del registro PnIFG para saber qué patilla del microcontrolador generó la interrupción.

6

1.4 El módulo de reloj

El módulo de reloj del microcontrolador tiene tres fuentes de señal de reloj para alimentar otras tres señales que sincronizan la CPU y los periféricos

Las fuentes de reloj son las siguientes:

• Un reloj que puede funcionar con cristales o resonadores cerámicos de baja frecuencia o de alta frecuencia (LFXTCLK). El modo se selecciona por software.

• Un reloj de alta frecuencia que ocupa cristales o resonadores cerámicos de alta frecuencia (XT2CLK).

• Un oscilador interno de características RC controlado digitalmente mediante registros de control (DCOCLK).

Con estas fuentes el módulo de reloj genera las siguientes tres señales:

• Reloj maestro (MCLK): que alimenta la CPU y el sistema y se puede generar a partir de la señal de baja frecuencia, la de alta frecuencia o el oscilador digital; que pueden dividirse por un factor de 1, 2, 4 u 8.

• Reloj de sub sistema (SMCLK): que alimenta a los periféricos seleccionados por software. Se puede generar a partir de la señal de baja frecuencia, la de alta frecuencia o el oscilador digital; que pueden dividirse por un factor de 1, 2, 4 u 8.

• Reloj auxiliar (ACLK): que alimenta a los periféricos seleccionados por software. Se genera a partir de la señal de baja frecuencia dividida por un factor de 1, 2, 4 u 8.

Esta flexibilidad en el sistema de reloj está especialmente indicada para ahorrar energía, ya que se puede ocupar un cristal de baja frecuencia, por ejemplo 32 KHz, para los periféricos, mientras la CPU se opera mediante el oscilador interno a una frecuencia que puede ir de los 800 KHz a los 8 MHz, dependiendo de la configuración y características del dispositivo en particular. Además para contrarrestar el efecto de corrimiento de frecuencia del oscilador interno se puede corregir periódicamente con la señal más estable proveniente del oscilador de baja frecuencia controlado por cristal.

8

1.5 El multiplicador por hardware

Algunos miembros de la familia de microcontroladores MSP430 cuentan con un módulo de multiplicación de 16 bits incorporado en su hardware, de forma que puede realizar multiplicaciones en tiempos que van desde un ciclo de reloj, dependiendo de la forma de direccionamiento de los parámetros. En particular el MSP430F149 cuenta con este periférico.

Puede realizar 4 tipos de operaciones: multiplicaciones con signo (MPYS), sin signo (MPY), multiplicaciones acumuladas con signo (MACS) y multiplicaciones acumuladas sin signo (MAC). El modo se selecciona al escribir el primer operando (OP1) en un registro distinto para cada modo, la multiplicación se ejecuta al escribir el segundo operando (OP2). Dependiendo del modo de direccionamiento del segundo operando el resultado puede estar disponible al siguiente ciclo de máquina. El resultado se obtiene en tres registros de 16 bits, uno almacena los 16 bits más bajos del resultado (RESLO). Los otros dos almacenan información que depende del tipo de operación (RESHI y SUMEXT). El diagrama se muestra en la Figura 1-3 [1].

Figura 1-3 Diagrama del multiplicador por hardware

9

1.6 Modos de bajo consumo

La familia de microcontroladores MSP430 tiene 5 modos de operación, uno activo (AM), y 4 de bajo consumo (LPMn) que se seleccionan escribiendo ciertos bits del registro de estado (SR). La diferencia entre cada uno de los modos es la cantidad de periféricos que quedan apagados, y el tiempo que le lleva al microcontrolador retomar su operación normal, que de todas formas no excede los 6 µS.

En cuanto al consumo el modo 3 en el que se detiene la CPU pero se mantiene en función un reloj de baja frecuencia para mantener un reloj de tiempo real, el consumo es de alrededor de 2 µA. En el modo 4, en que se detiene toda actividad pero se mantiene el estado de la memoria RAM el consumo es de tan sólo 0,2 µA.

Para obtener el mejor rendimiento en sistemas portátiles el microcontrolador es llevado al modo 3 y mediante interrupciones generadas por uno de los temporizadores se activa momentáneamente la CPU para realizar las operaciones del programa, luego se vuelve a llevar al modo de bajo consumo.

1.7 Los temporizadores

Existen tres temporizadores disponibles en el microcontrolador MSP430F149, uno que realiza la función de perro guardián (watchdog). Un temporizador/contador que cuenta con 3 registros de captura o comparación y otro que cuenta con 7 registros de captura o comparación. Más detalles a continuación:

1.7.1 El temporizador watchdog

La principal función del temporizador de watchdog es reiniciar el procesador después de una falla en el software o al no producirse un evento esperado, al completarse un período de tiempo determinado (timeout).

Es decir, el programador selecciona un tiempo adecuado y dentro del programa reinicia periódicamente el temporizador, cuando el software se bloquee por alguna razón el procesador será reiniciado por el temporizador de watchdog al término del ciclo actual del temporizador.

10

Todo programa para este microcontrolador debe comenzar configurando o desactivando el temporizador de watchdog, ya que el microcontrolador se reinicia con esta función activada de forma predeterminada.

Si no se utiliza como temporizador de watchdog el temporizador se puede utilizar para generar intervalos de tiempo, por ejemplo para generar interrupciones.

El período del temporizador se fija seleccionando la fuente de reloj que puede ser el reloj auxiliar (ACLK) o el reloj de sub sistemas (SMCLK) y el factor de división que puede ser 62, 512, 8192 ó 32768. Los valores son configurados mediante el registro de control del temporizador de watchdog (WDTCTL).

1.7.2 Los Temporizadores A y B

Estos son temporizadores o contadores con registros de captura o comparación con la capacidad de generar múltiples salidas o interrupciones.

La principal diferencia entre los temporizadores A y B es que el segundo tiene la posibilidad de seleccionar la longitud del registro temporizador entre 8, 10, 12 ó 16 bits, en tanto el primero tiene un registro de longitud fija de 16 bits. Además el temporizador B tiene 7 registros de captura o comparación, en tanto el A tiene sólo 3.

Por cada uno de los registros de captura o comparación se tiene una etapa de salida. Además los registros de captura o comparación del temporizador B pasan por un buffer adicional y se pueden agrupar.

En modo de temporizador las fuentes del reloj pueden ser las señales ACLK, SMCLK o una señal externa a través de los pines TACLK (TBCLK) o INCLK. A su vez la fuente de reloj elegida puede ser dividida por un factor de 2, 4 u 8 mediante los bits IDx del registro de control TACTL (TBCTL). Puede funcionar en uno de cuatro modos, seleccionado con los bits MCx

11

Tabla 1-3 Modos del contador

MCx Modo Descripción

00 Detenido El temporizador está detenido

01 Arriba El temporizador cuenta desde cero hasta TACCR0(TBCL0)

10 Continuo Cuenta desde cero hasta 0xFFFF para el temporizador A o los bits indicados por TBCNTLx y parte desde 0 nuevamente

11 Arriba y abajo Cuenta desde cero hasta 0xFFFF para el temporizador A o los bits indicados por TBCNTLx y hacia cero nuevamente

Para mayor claridad se muestran las siguientes figuras del manual del usuario del microcontrolador.

Figura 1-4 Modos del temporizador A como temporizador/contador (a) Modo hacia arriba, (b) modo continuo, (c) modo hacia arriba y abajo.

12

Figura 1-5 Modos del temporizador B como temporizador/contador (a) Modo hacia arriba, (b) modo continuo, (c) modo hacia arriba y abajo.

En cada una de las situaciones anteriores se tiene la posibilidad de generar interrupciones (serán tratadas más adelante).

El modo de captura se utiliza para capturar eventos temporales, como medidas de velocidad o tiempo. Primero el usuario selecciona la señal interna o externa que provocará la captura y el canto de subida, bajada o ambos. Cuando se produce la condición seleccionada el valor actual del contador TAR (TBR) se copia al registro de captura programado (3 módulos para el temporizador A y 7 módulos para el B), al mismo tiempo al flag de interrupción del módulo correspondiente se le escribe el valor uno, produciéndose una interrupción si está habilitada.

El modo de comparación se utiliza para generar señales de modulación de ancho de pulso (PWM) o para generar interrupciones a intervalos específicos. Cuando el valor del contador TAR (TBR) llega a TACCRx (TBCCRx) se escribe un uno en el flag de interrupción del temporizador y se produce la salida según se halla programado. En este punto los dos temporizadores difieren levemente debido al doble buffer del temporizador B. En el temporizador B se puede elegir el momento en que se actualizan los

13

latch de comparación con el valor de los registros de comparación, que son los que el usuario manipula. Además se puede agrupar varios latch para su actualización simultánea. El momento se refiere al valor del contador TBR.

Los bloques de salida se ocupan en el modo de comparación para generar 7 tipos de salidas seleccionables por el usuario a través de los 3 bits OUTMODx de los registros de configuración de los módulos de salida TACCTLx (TBCCTLx).

Como ejemplo se muestra en la figura 1.6 el temporizador B en modo contador continuo y las salidas que se obtienen en cada uno de los 7 modos, EQUx son señales internas.

Figura 1-6 Salidas del temporizador B en modo contador continuo

Asociado a cada uno de los temporizadores existen dos vectores de interrupción, el primero corresponde a interrupciones generadas por el flag CCIFG de TACCR0 (TBCCR0), el segundo corresponde a interrupciones generadas por los restantes flags CCIFG de los registros TACCRx (TBCCRx).

14

Los flags se activan en modo de captura cuando un valor es capturado al registro correspondiente y en modo de comparación el flag responde cuando el valor del contador alcanza el valor del registro correspondiente.

Asociado al segundo vector de interrupción existe un registro, TAIV (TBIV), que indica el módulo de captura o comparación que generó la interrupción, cada uno escribe un valor en el registro que puede utilizarse en instrucciones de salto para llegar a la rutina correspondiente.

1.7.3 El comparador analógico y los conversores análogo a digital

El microcontrolador contiene un comparador de voltaje analógico, cuyo esquema se muestra en la Figura 1-8, obtenido del manual del usuario del microcontrolador.

Las dos entradas son seleccionables por el usuario entre señales externas o niveles generados internamente en el procesador de 0.25Vcc, 0.5Vcc o el voltaje de umbral de un transistor de aproximadamente 0,55 V.

Cuando el valor del voltaje en el terminal + es mayor al del terminal – la señal de salida CAOUT va a estado alto. La salida puede o no ser filtrada con un filtro pasabajos RC interno para aminorar las oscilaciones que se producen cuando las señales son muy parecidas. La señal de salida está conectada al primer bloque de captura del temporizador A para realizar mediciones de tiempo, además puede generar interrupciones con el flag CAIFG en los cantos de subida o bajada de la señal CAOUT. El efecto de la utilización del filtro se puede ver en la Figura 1-7.

Figura 1-7 Efecto del filtro pasabajos en la salida

15

Figura 1-8 Diagrama del comparador analógico

Una de las características distintivas de la familia de microcontroladores es la incorporación de conversores análogo a digital. El MSP430F149 tiene un conversor de 12 bits con una tasa de muestreo de casi 200 mil muestras por segundo, el inicio de la conversión se puede realizar por software o por señales provenientes de los temporizadores; el término de la conversión puede generar interrupciones para alertar al procesador; la referencia positiva se puede seleccionar entre una señal externa o interna fija de 1.5 V ó 2.5 V; la referencia negativa se puede seleccionar entre una señal externa o la tensión de tierra negativa.

El sistema tiene 8 canales configurables independientemente, además de 4 señales internas provenientes de un sensor de temperatura en el procesador y los niveles de los voltajes de referencia. Tiene un buffer de 16 direcciones de memoria configurables para almacenar las muestras antes de alertar al procesador. Tiene múltiples fuentes de interrupción atendidas por el mismo vector de interrupciones, pero diferenciables con el registro de interrupción que almacena un valor diferente para cada fuente. El diagrama completo del módulo conversor como aparece en el manual del usuario se muestra en la Figura 1-9.

16

Figura 1-9 Diagrama del conversor análogo a digital

El resultado de la conversión asume el valor de 0xFFF cuando la señal de entrada (Vin) es igual o superior a VR+ y toma el valor de 0x000 cuando la señal de entrada es igual o inferior a VR-. Para otros valores la fórmula de conversión es:

−+

−

−−

×=RR

RinADC VV

VVN 4096

El reloj puede provenir de SMCLK, MCLK, ACLK, o de un reloj generado internamente ADC12CLK que está en el rango de los 5 MHz, cualquiera de las fuentes elegidas se puede dividir por un factor de 1 hasta 8.

17

La conversión se inicia en el canto de subida de la señal interna SHI, que se selecciona entre: el bit ADC12SC controlado por software, o la etapa de salida 1 del temporizador A, o la 0 o la 1 del temporizador B. Esta señal a su vez controla la señal SAMPCON que sincroniza las etapas de muestreo y retención y la etapa de conversión que toma 13 ciclos del reloj ADC12CLK. En la Figura 1-10 se ve un ciclo completo de muestreo y conversión.

Figura 1-10 Tiempos de muestreo y conversión

El conversor puede funcionar en uno de cuatro modos seleccionados con los bits CONSEQx del registro de control ADC12CTL1, sus características se resumen en la Tabla 1-4.

Tabla 1-4 Modos de operación del conversor análogo a digital

CONSEQx Modo Operación

00 Un canal una conversión

Un canal se convierte una sola vez

01 Secuencia de canales

Una secuencia de canales es convertida una vez

10 Repetir un canal Un canal se convierte repetidas veces

11 Repetir secuencia de canales

Una secuencia de canales se repite varias veces

18

Las 16 direcciones de memoria que almacenan los datos ADC12MEMx se configuran con sus correspondientes 16 registros de control ADC12MCTLx. Se puede configurar independientemente para cada una el canal y la fuente para las referencias. Además el bit EOS indica el fin de secuencia cuando se selecciona una conversión secuencial. La conversión comienza usando el registro de control seleccionado con los bits CSTARTADDx del registro ADC12CTL1 y en caso de una conversión secuencial continúa con los registros de control restantes hasta encontrar el bit EOS. Si no se utiliza una conversión secuencial el único registro utilizado es el indicado por CSTARTADDx.

El módulo puede generar 18 condiciones de interrupción: ADC12IFG0-ADC12IFG15, que se activan cuando la correspondiente memoria es cargada con un dato, ADC12OV activada cuando se sobrescribe una zona de memoria, y ADC12TOV si se quiere iniciar una conversión antes del término de la actual. Todas las interrupciones, si están habilitadas, van al mismo vector de interrupción, la fuente específica se distingue con el valor almacenado en el registro ADC12IV, que puede utilizarse para saltar rápidamente a la rutina de atención que corresponda.

19

Capítulo 2 La tarjeta de desarrollo EasyWeb II

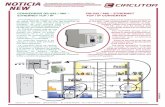

Para el trabajo en el laboratorio se eligió la tarjeta de desarrollo EasyWeb II fabricada por Olimex, ver Figura 2-1. Se escogió esta tarjeta debido a la gran cantidad de periféricos incorporados en relación al costo de la misma. Otros fabricantes ofrecen tarjetas de similares características pero a más del doble del precio.

A grandes rasgos consiste de un microcontrolador MSP430F149, con un cristal de 8 MHz, un controlador de red CS8900A de Cirrus Logic con los componentes externos correspondientes, un cambiador de niveles RS232 con su respectivo conector DB9 hembra, un display de cristal líquido alfanumérico de 16x2 caracteres, cuatro pulsadores, cuatro entradas optoacopladas, 2 salidas activadas por relé, un zumbador, una memoria flash serial de 64 KB en la tarjeta, conector para dispositivos iButton de Dallas Semiconductor, patilla de entrada del reloj del temporizador A disponible en conector, conector para los conversores análogo a digital del microcontrolador, conector para los pines JTAG del microcontrolador.

Figura 2-1 Tarjeta de desarrollo

2.1 Descripción del circuito

Los nombres de los buses de datos y su correspondiente patilla del microcontrolador utilizados en la presente sección se refieren al diagrama de la Figura 2-2.

20

Figura 2-2 Esquema de conexiones del microcontrolador

La tarjeta se alimenta con una fuente de corriente continua de 12 V que se conecta directamente a los relés y a los reguladores de voltaje de tres terminales. Mediante un circuito LM317L se generan los 3,6 V que utiliza el microcontrolador, la memoria serial, el cambiador de niveles RS232, los optoacopladores y las resistencias de pull-up conectadas a los pulsadores. Además se generan 3,3 V, también con un circuito LM317 para el controlador ethernet CS8900A. Con un regulador 78L05 se generan 5 V para el display de cristal líquido. El esquemático correspondiente a las fuentes de tensión se muestra en la Figura 2-3.

21

Figura 2-3 Diagrama de fuente de alimentación

Los cuatro pulsadores se conectan a los puertos de entrada y salida del microcontrolador utilizando resistencias de pull up para mantener los niveles lógicos estables [1] como se puede ver en la Figura 2-4.

22

Figura 2-4 Conexión de pulsadores

Debido a que el dispositivo acepta niveles de tensión de entrada hasta el valor de VCC las entradas digitales se conectan al microcontrolador mediante optoacopladores. Para ello se utiliza el circuito 4N37 de Fairchild Semiconductor, ver Figura 2-5.

Figura 2-5 Esquema de optoacoplador

La entrada al optoacoplador se conecta mediante un led indicador y una resistencia de limitación de corriente de 330 Ω, la hoja de características del dispositivo indica 100 mA como nivel de corriente directa de forma segura en el emisor [4], lo que indica que la tarjeta puede aceptar un nivel de tensión de hasta 33 V de forma segura. El esquema se puede ver en Figura 2-6.

23

Figura 2-6 Conexión de optoacopladores

En la tarjeta se encuentran disponibles 2 salidas activadas con relé lo que posibilita manejar cargas de hasta 10 A a 220 V. Como es usual se tiene una conexión normalmente conectada y otra normalmente abierta. Para activar los relés se utiliza un transistor a efecto de amplificar la corriente de la salida del microcontrolador a un nivel suficiente para estimular los relés, además se cuenta con un led para indicar cuando el relé está activo, el diagrama de conexión se muestra en la Figura 2-7

Figura 2-7 Conexión de relés

La memoria flash serial se conecta directamente a los pines del microcontrolador. Debido a que este microcontrolador no cuenta con el protocolo Inter Integrated Circuit (I2C), se debe programar por software y utilizar pines de entrada y salida estándar para generar las señales necesarias, que son una línea de reloj (SCL) y otra de datos (SDA). Ver Figura 2-8.

24

Figura 2-8 Conexión a la memoria Flash

El módulo de cristal líquido GDM1602K de Xiamen Ocular se conecta directamente al microcontrolador por medio de un conector montado en la placa de circuito. En este caso la comunicación se realiza por medio de 6 pines. Cuatro de ellos llevan los datos de 8 bits, trasmitiendo los cuatro bits altos del dato seguido de los 4 bits bajos, sincronizados mediante una señal de control (E). El esquema se muestra en la Figura 2-9.

Figura 2-9 Conexión del display de cristal líquido

La comunicación serial del microcontrolador con dispositivos que siguen la norma RS232 se realiza con dos señales TX y RX conectadas directamente a los pines del puerto serie universal 1 del microcontrolador, los niveles de tensión se adaptan mediante el circuito integrado MAX3232 según el esquema que se puede ver en la Figura 2-10. Utilizando terminología del protocolo RS232 la tarjeta está conectada como un Data Communications Equipment (DCE), porque presenta un conector hembra y el pin de transmisión es el 2 y el de recepción es el 3.

25

Figura 2-10 Conexión del puerto serial

Para conectar a un PC se debe conectar un cable con un conector hembra por un lado que se conecta al puerto serial del PC (Data Communication Equipment, DCE), y un conector macho por el otro que se conecta a la tarjeta. Las conexiones son del pin 2 de uno al pin 2 del otro y del pin 3 de uno al pin 3 del otro, y el cable de tierra entre los pines 5 de cada conector como se muestra en la Figura 2-11.

Figura 2-11 Conexiones de cable serial

En la tarjeta se encuentran disponibles dos conectores que permiten acceso a las entradas de los conversores análogo a digital del microcontrolador. Además se puede acceder a los pines de transmisión serial, a los pines de comunicación con la memoria flash, al pin de reset del microcontrolador, al pin que lleva el reloj auxiliar generado por el módulo de reloj del microcontrolador en P2.0 y a los niveles de tensión generados por los reguladores. Ver Figura 2-12

26

Figura 2-12 Esquema de conectores

El controlador ethernet CS8900A se conecta mediante un bus ISA estándar, pero además tiene la capacidad de utilizar un bus de datos de 8 bits, en el que se multiplexan los bytes altos y bajos de los datos de 16 bits que ocupa el controlador. Esta característica lo hace especialmente indicado para utilizarse en sistemas embebidos, así se reduce el número de pines dedicados a la interconexión a sólo 14, que son: 8 para transmisión de datos, 4 para indicar la dirección de memoria para escritura o lectura (los restantes 16 se conectan directamente a tierra o VCC para configurar la dirección base), y 2 para señalización de lectura y escritura. El controlador ethernet maneja dos leds que indican enlace establecido y actividad en el enlace. La conexión al medio ethernet se realiza mediante un transformador de aislamiento y un conector RJ45 estándar. El diagrama se muestra en la Figura 2-13.

27

Figura 2-13 Conexión del controlador ethernet

Por último se encuentran en la placa de circuito un zumbador conectado directamente a dos pines del puerto 4 del microcontrolador, la frecuencia del sonido se puede controlar por software. Además los cuatro pines del puerto JTAG se encuentran en un conector para facilitar su interconexión con la herramienta de interfaz hacia el puerto paralelo del PC. Esta herramienta es relativamente sencilla, su principal propósito es de buffer y aislación para los pines que se ocupan en la comunicación serial, además tiene la posibilidad de ocupar las señales no utilizadas del puerto paralelo del PC para generar 3,3 V que pueden alimentar un circuito mientras se programa o emula, en el caso particular de la tarjeta EasyWeb II es la tarjeta la que alimenta al programador, ya que no se podría obtener suficiente corriente desde el puerto paralelo para alimentar al programador y a la tarjeta. En la Figura 2-14 se ve la apariencia de la herramienta de programación y en la Figura 2-15 su diagrama esquemático.

29

Capítulo 3 Introducción a protocolos de comunicación entre dispositivos

En el presente capítulo se pretende introducir algunas formas y protocolos de comunicación entre dispositivos utilizados en sistemas con microcontrolador.

Debido a la falta de un estándar para interconectar circuitos integrados dentro de la misma placa de circuito o a cortas distancias, algunos fabricantes han elaborado sistemas propietarios, lo que ha generado una multiplicidad de protocolos incompatibles entre sí, entre los más ampliamente utilizados se encuentran: SPI (Serial Peripheral Interface) de Motorola, Microwire de National Semiconductor [5] e Inter Integrated Circuit (I2C) de Philips. Además existen muchos otros protocolos para aplicaciones específicas, por ejemplo en la industria automotriz se han desarrollado una gran cantidad de protocolos para comunicar dispositivos, solo por nombrar algunos: Controller Area Network (CAN), ISO11783, Local Interconnect Network (LIN), Media Oriented Systems Transport (MOST).

La mayoría de ellos comparte dos características básicas, la de operar con los mismos niveles de voltaje que los dispositivos que interconectan, es decir, no se necesitan cambiadores de nivel; y ser sincrónicos, lo que permite una comunicación confiable a pesar de las diferencias que puedan producirse en los relojes de cada dispositivo, así un corrimiento en frecuencia no producirá errores en la transmisión o recepción, debido a que ambos dispositivos están sincronizados con una señal de reloj única para la comunicación.

A continuación se detallarán las diferencias, entre Microwire, SPI e I²C, comparando sus ventajas y desventajas según la aplicación

Microwire y SPI son muy parecidos [6], ambos consisten en 3 terminales que llevan datos seriales de entrada, de salida y señal de reloj, debido a esto son full duplex por naturaleza. Los dispositivos que interconectan deben compartir los mismos niveles de tierra y VCC. Son útiles en ambientes en los que existe un dispositivo maestro (el que genera la señal de reloj) y uno o varios esclavos. Debido a que el protocolo no incluye direccionamiento de dispositivos el maestro debe habilitar al dispositivo al que se quiere comunicar a la vez que deshabilita a los demás, esto representa una gran desventaja cuando existe más de un esclavo ya que aumenta la cantidad de pines necesarios en el microcontrolador (maestro) necesarios para la comunicación. Una de las ventajas de estos protocolos es que son sensibles al canto de la señal, lo que la hace un poco más inmune al ruido

30

que si fuera activada por nivel. La velocidad de transmisión es uno de los puntos fuertes de estos protocolos, en sucesivas revisiones de ellos se ha ido subiendo la velocidad máxima hasta los 3 Mbits/s para Microwire y 10 Mbits/s en el caso de los últimos dispositivos SPI [6].

3.1 El protocolo I²C y la memoria EEPROM serial 24LC515

I²C [7] es un bus serial, half duplex de 2 cables bidireccionales: datos (Serial Data, SDA) y señal de reloj (Serial Clock, SCL); puede interconectar uno o varios maestros (el dispositivo que comienza la comunicación y genera la señal de reloj) con uno o varios esclavos (que son direccionados por el maestro).

El protocolo incluye un campo de direccionamiento de 7 ó 10 bits según el modo que se utilice, lo que permite tener varios dispositivos conectados al mismo bus. Incluye la posibilidad de que exista más de un maestro en el bus mediante detección de colisiones y control de acceso al bus. La tasa de transmisión es de 100 Kbits/s en el modo estándar, de 400 Kbits/s en el modo rápido, y recientemente el modo de alta velocidad aumentó la tasa máxima de transmisión a 3,4 Mbits/s, pero actualmente existen pocos dispositivos que soporten esta velocidad.

La comunicación comienza con las dos líneas (SDA y SCL) en estado alto. Luego el maestro señaliza el comienzo de la comunicación escribiendo un cero en la línea de datos mientras la señal de reloj sigue en estado alto.

Enseguida envía los 7 bits de dirección del dispositivo esclavo con el que se quiere comunicar, el formato de transmisión comienza con el bit más significativo primero y se envía en grupos de ocho bits. El octavo bit del primer octeto enviado le indica al esclavo si se debe preparar para recibir o enviar información, un uno indica recepción por parte del maestro.

A continuación el esclavo debe responder con un bit de reconocimiento (ACK), tras lo cual comienza la comunicación, transmitiendo un byte a la vez y con el bit de ACK, un cero, por parte del dispositivo que recibe la información.

Al finalizar la comunicación el maestro debe generar la condición de término, que consiste en una transición de 0 a 1 de la señal SDA mientras la señal SCL está en 1. Se recuerda que este protocolo es sensible al nivel de la señal por lo que la información en SDA debe ser estable mientras SCL se encuentra en estado alto, con la única excepción de las condiciones de inicio

31

y fin de transmisión. Un ejemplo completo de una transferencia se puede ver en la Figura 3-1.

Figura 3-1 Comunicación I²C

El protocolo permite a un dispositivo esclavo interrumpir la transmisión cuando no es lo suficientemente rápido para procesar la información que está recibiendo, esto lo logra escribiendo un cero en la línea de reloj (SCL) después de generar un ACK al transmisor. Al detectar esta condición el transmisor censa la línea de reloj hasta que el receptor devuelve la línea al estado alto. Además el maestro tiene permitido disminuir la frecuencia del reloj para hacer más lenta la comunicación.

En el caso de los modos rápidos y de alta velocidad, que pueden utilizar un campo de direccionamiento de 10 bits, esta condición se indica mediante un patrón especial en el primer octeto de la dirección, junto con el bit de lectura o escritura; y en el segundo byte se envía el resto de la dirección. Las direcciones de los dispositivos esclavos son asignadas por un comité, y el protocolo es licenciado por Philips Semiconductors a los fabricantes que quieran incorporarlo a sus productos.

En algunos casos un dispositivo puede tener una parte de la dirección fija y otra programable, con el objetivo de tener varios dispositivos iguales conectados al mismo bus. Este es el caso de la memoria serial 24LC515 de Microchip [8] incorporada en la tarjeta de desarrollo EasyWeb II. Está preparada para funcionar en modo rápido, es decir, con una frecuencia de reloj máxima de 400 KHz y tiene dos pines especiales para indicar la dirección del dispositivo, por lo que se puede tener hasta cuatro de ellas conectadas al mismo bus, con un total de 64KB por cuatro, es decir 256 KB en total. Ajustándose al estándar I²C el primer byte tiene la estructura que se puede ver en la Figura 3-2.

32

Figura 3-2 Byte de control

Comienza con la condición de Start del protocolo seguido de la dirección del dispositivo que en este caso consiste de los bits 1010, seguido de un bit que indica el bloque de 32 KB (alto o bajo) al que se desea acceder, seguido de dos bits que sirven para direccionar hasta cuatro memorias conectadas al mismo bus, el byte concluye con el bit de lectura o escritura.

El dispositivo esclavo que se está direccionando debe reesponder con el bit de ACK en el noveno ciclo de reloj. A continuación el dispositivo maestro envía dos bytes con los 15 bits de la dirección de memoria que se quiere acceder, estos 15 bits más el bit indicador de bloque permiten direccionar los 64 KB de la memoria. En caso de existir más de una memoria en el mismo bus los bits A0 y A1 correctamente conectados en las memorias expanden la cantidad máxima direccionable hasta 256 KB. La secuencia completa de direccionamiento se puede ver en la Figura 3-3.

Figura 3-3 Direccionamiento de la memoria

Después de cada byte el dispositivo esclavo responde con ACK. En el caso de una escritura en memoria (el bit de R/W en cero), el maestro envía el dato a escribir, y el esclavo responde con ACK, ver Figura 3-4, si no se desea

33

escribir más datos el maestro genera la condición de STOP tras lo cual el 24LC515 comienza el ciclo de escritura en el arreglo; en caso de que se desee escribir una secuencia de datos se envían hasta 64 bytes en forma secuencial, los que son almacenados por la memoria en un buffer interno, al recibir la condición de STOP por parte del maestro, la memoria comienza el ciclo de escritura de los bytes desde el buffer hacia el arreglo, ver Figura 3-5.

Figura 3-4 Escritura de un byte

Figura 3-5 Escritura de una página de hasta 64 bytes

Mientras el dispositivo está ocupado realizando una operación de escritura no responderá con ACK a un direccionamiento, condición que le sirve al maestro para saber cuando el dispositivo está listo para otra operación, el diagrama de flujo del proceso necesario se muestra en la Figura 3-6.

34

Figura 3-6 Diagrama de flujo de fin de escritura

El procedimiento para efectuar una lectura en la memoria es similar a la escritura, pero se distinguen dos situaciones:

Si se desea acceder a una dirección aleatoria dentro de la memoria se debe enviar primero en una operación de escritura (R/W en 0) la dirección específica, tras lo cual se puede ejecutar una operación de lectura (R/W en 1) y el dispositivo envía el dato requerido; en respuesta el maestro puede generar un ACK si se quiere leer posiciones sucesivas de memoria (ver Figura 3-8), u omitir el ACK y enviar una condición de STOP para concluir la transmisión (ver Figura 3-7). El circuito integrado contiene un puntero que almacena la última dirección de memoria accesada, por lo que se puede realizar operaciones de lectura de la dirección actual sin enviar una nueva dirección (ver Figura 3-9), esta característica permite realizar una lectura secuencial de todo el bloque (32 KB) en forma sucesiva.

Si

No

Envío de comando de escritura

Envío condición de STOP para comenzar

ciclo de escritura

Enviar byte de control con R/W en cero

¿Se recibe ACK?

Siguiente operación

35

Figura 3-7 Lectura de posición aleatoria

Figura 3-8 Lectura de posiciones sucesivas

Figura 3-9 Lectura de dirección actual

El protocolo especifica que las señales SDA y SCL deben operarse con conexiones de colector abierto para poder generar un wired AND en el bus, en caso de que varios maestros quieran iniciar una comunicación simultáneamente. El MSP430 es capaz de emular este tipo de conexión en cualquiera de los pines de entrada y salida [9]. Esto se logra escribiendo un cero en el registro de salida del puerto correspondiente y manejando el nivel en la salida mediante el registro de dirección. Si se requiere un cero en la salida, el pin se configura como salida, con lo que el valor de 0 escrito en el registro se refleja en la salida. Si se quiere un 1 en la salida el pin se configura como entrada, de esta forma la resistencia de pull up interna fija el nivel en 1 de forma estable. La lectura se efectúa siempre mediante el registro de entrada del puerto.

36

3.2 Los dispositivos iButton de Dallas Semiconductors y el protocolo propietario 1-Wire

Dallas Semiconductors desarrolló una forma de interconectar dispositivos, por ahora sólo fabricados por ellos, pero con la posibilidad de licenciar a otros fabricantes. La principal característica de este protocolo es que sólo necesita 1 línea de comunicación, además de una tierra común, que lleva los datos de la comunicación y le provee energía al dispositivo. Además cada dispositivo tiene un código de 64 bits propio, lo que permite tener varios conectados al mismo bus y direccionarlos individualmente. Entre la gama de dispositivos disponibles se encuentran conversores análogo a digital, sensores de temperatura, potenciómetros digitales, memoria de variados tipos, interruptores digitales, y otros. Con esto este protocolo no es más que otro protocolo de comunicación serial más, pero los circuitos pueden venir tanto en encapsulados típicos para circuito impreso como en la forma de encapsulado iButton en que se obtienen características especiales.

Este encapsulado consiste en un montaje de dos piezas de acero circulares de 16 mm de diámetro (ver Figura 3-11) que contienen en su interior el circuito integrado y que además de protección sirven para comunicar la tierra y la línea 1-Wire del dispositivo hacia el exterior como se muestra en la Figura 3-10.

Figura 3-10 Esquema eléctrico de iButton

37

Figura 3-11 Apariencia de un dispositivo iButton

Entre la gama de dispositivos disponibles existen algunos que sólo contienen su código de identificación, termómetros digitales, termómetros con almacenamiento de las muestras tomadas a intervalos programables (almacenadas en RAM y alimentada por batería de litio interna), memorias no volátiles de variados tipos, relojes de tiempo real, memorias protegidas con algoritmos de encriptación de alto nivel, microcontroladores con máquina virtual Java.

Además existen puntas de prueba para conectarlos a microcontroladores o computadores (con adaptadores para puerto serial, paralelo o USB). La característica de portabilidad de estos dispositivos y su robusto encapsulado permite una gran variedad de aplicaciones, desde control de acceso utilizando su código de identificación, almacenamiento de información sensible, control in situ de la temperatura. Los que cuentan con encriptación de datos están pensados para utilizarse como medio de pago electrónico. El microcontrolador con máquina virtual Java ejecuta aplicaciones principalmente orientadas a la encriptación y certificación (firma electrónica, acreditación de identidad en transacciones).

La interconexión con microcontroladores se realiza mediante una línea conectada a VCC a través de una resistencia de Pull-up, en estado de reposo el nivel de la línea es alto, cuando el dispositivo iButton se pone en contacto se carga un condensador interno, lo que le provee la energía necesaria para su funcionamiento. Existen algunos que necesitan un nivel mayor de voltaje para realizar algunas operaciones (conversión de temperatura, grabado de memoria EEPROM), para ellos es necesario sacrificar una línea de control en el dispositivo maestro para manejar un transistor que conecta la línea de comunicación directamente a VCC (saltando la resistencia de pull-up) después de dar la instrucción que requiere mayor voltaje.

El protocolo 1-Wire es half duplex y asincrónico por lo que las rutinas para controlar los tiempos de duración de cada pulso deben ser lo más precisas posibles y estar dentro de los rangos de cada dispositivo en particular. La comunicación comienza con el microcontrolador enviando un pulso (cero) de reset en la línea a lo que el dispositivo responde mediante un

38

pulso avisando su presencia como se muestra en la Figura 3-12, obtenida de las hojas de características de un termómetro digital iButton.

Figura 3-12 Pulso de reset y presencia

La escritura se realiza en ranuras de tiempo que miden entre 60 y 120 µS con un período mínimo de recuperación de 1 µS, el dispositivo iButton muestrea la línea aproximadamente en la mitad de la ranura. La escritura comienza con el dispositivo maestro escribiendo un cero en la línea, si se quiere enviar un cero al dispositivo iButton se mantiene el cero durante todo el período, si se quiere enviar un uno se sube la línea después 15 µS. De las hojas de características mencionadas se obtuvo la Figura 3-13.

Figura 3-13 Escritura en dispositivos iButton

La lectura también se realiza en ranuras de tiempo de entre 60 y 120 µS con un período de recuperación mínimo de 1 µS. El dispositivo maestro comienza enviando un pulso de 1 µS y en seguida cede el control de la línea al dispositivo iButton, el que responde colocando un cero o un uno según corresponda, el maestro debe muestrear la línea después de 15 µS del inicio de la ranura de tiempo, en la figura 3-14 se muestra un esquema del proceso.

39

Figura 3-14 Lectura desde dispositivos iButton

La mayor dificultad de implementar este protocolo en microcontroladores radica en la generación de los tiempos necesarios. Las rutinas aunque simples dependerán de factores como el reloj del microcontrolador, posibles interrupciones, etc.

En forma general se puede resumir las operaciones en los siguientes diagramas de flujo:

Figura 3-15 Generación de reset y estado de dispositivo

Escribir cero en la línea

Generar retardo de 480 µS

Volver la línea a estado alto

Retardo de 70 µS

Leer la línea y determinar presencia o ausencia de

dispositivo

40

Figura 3-16 Lectura de un bit desde dispositivo iButton

Figura 3-17 Escritura de un bit en dispositivo iButton

No

Si

Escribir cero en la línea para comenzar la ranura de tiempo

Mantener en estado bajo

Mantener estado hasta el fin de la ranura de tiempo

Se quiereescribir un “1”

Regresar la línea a estado alto

Regresar la línea a estado alto

Escribir cero en la línea para comenzar la ranura de tiempo

Volver la línea a estado alto

Retardo de 15 µS desde el comienzo de la ranura

Leer estado de la línea, esperar hasta el fin de la ranura de tiempo y retornar estado

41

Cada dispositivo en particular tiene su repertorio de instrucciones, por lo que la programación de una aplicación debe realizarse mediante sus hojas de características. Existen algunas instrucciones compartidas como: leer el código identificatorio, o generar un CRC para comprobar los datos transmitidos.

42

3.3 Control de un módulo de cristal líquido alfanumérico

La comunicación entre el microcontrolador y el display de cristal líquido se realiza indirectamente a través de un controlador montado en el módulo. Esta es una práctica habitual para liberar pines de conexión en el microcontrolador y dejar el trabajo de desplegar la información y refrescar la pantalla a un controlador especializado. En el caso del módulo disponible en la tarjeta de desarrollo el controlador es un KS0066U.

La interconexión se realiza mediante un bus paralelo que puede ser de 4 u 8 bit, más 3 señales de control. Además el módulo ocupa otras tres señales para llevar tierra, Vcc y el voltaje de control para el contraste. Sus funciones se detallan en la Tabla 3-1.

Tabla 3-1 Función de pines del módulo de cristal líquido

Número de pin Función

1 Tierra

2 VCC

3 Voltaje de control de contraste

4 “R/S” selección de instrucción o registro

5 “R/W” lectura escritura de registros

6 “E” sincronización en modo de 4 bits

7 - 14 D0-D7 4 u 8 bits de datos

En el caso de la tarjeta de desarrollo utilizada se utiliza la conexión con un bus de 4 bits, se transmiten en forma serial los cuatro bits altos del dato seguidos de los 4 bits bajos, sincronizados con la señal E, por simplicidad la señal del módulo R/W se encuentra cableada a tierra, de modo que sólo es posible realizar escrituras en los registros del controlador, la indicación de si el dato transmitido corresponde a un dato o una instrucción se expresa mediante la señal R/S. Así que la interconexión entre el microcontrolador y el controlador del módulo se realiza con 6 señales, conectadas directamente a puertos del microcontrolador.

43

Los comandos se envían al controlador mediante una palabra de 8 bits, las instrucciones disponibles (sólo las que escriben registros en el controlador) se resumen en la tabla

Tabla 3-2 Comandos del módulo de cristal líquido

R/S R/W D7 D6 D5 D4 D3 D2 D1 D0 Descripción

0 0 0 0 0 0 0 0 0 1 Borrar display

0 0 0 0 0 0 0 0 1 * Regresar cursor al comienzo

0 0 0 0 0 0 0 1 ID S Fijar dirección de movimiento cursor y desplazar display

0 0 0 0 0 0 1 D C B Habilitar display, cursor e intermitencia del cursor

0 0 0 0 0 1 SC RL * * Mover cursor/desplazar display

0 0 0 0 1 DL N F * * Fijar largo de la interfaz

0 0 0 1 A A A A A A Mover cursor en RAM

0 0 1 A A A A A A A Mover cursor a display

0 1 BF * * * * * * * Interrogar el bit de ocupado

1 0 D D D D D D D D Escribir carácter al display en posición actual

1 1 D D D D D D D D Leer carácter desde display en posición actual

La descripción de cada bit es la siguiente:

Fijar dirección de movimiento del cursor:

I/D: Incrementa/decrementa la posición del cursor en el display después de ecrbibir un byte

S: Desplaza el display después de escribir un byte

Habilitar display/cursor:

D: Enciende el display

C: Enciende el cursor

44

B: Cursor parpadeante

Mover cursor, desplazar el display:

S/C: Activa desplazamiento del display

R/L: Dirección del desplazamiento (0 izquierda, 1 derecha)

Fijar largo de la interfaz:

DL: Fijar ancho del bus (0= 4 bits, 1=8 bits)

N: Número de líneas del display (0=1 línea, 1=2 líneas)

F: Fuente para los caracteres (0=5x8, 1=5x11)

Interrogar flag de ocupado:

BF: En 1 cuando el controlador está ocupado

Mover el cursor en RAM/display:

A: Dirección de memoria

Leer, escribir dato al display:

D: Byte de información

45

Una de los problemas de no poder interrogar el flag de ocupado (porque el pin de R/W está cableado a tierra) es que la operación se torna más lenta, ya que hay que esperar un tiempo extra entre cada instrucción. De las hojas de características del controlador se obtiene que las instrucciones de borrado del display y regreso del cursor son las que más tiempo toman: 1,5 mS; el resto de las instrucciones toman menos de 50 µS. Pero el fabricante de la tarjeta de desarrollo recomienda 100 mS y 10 mS respectivamente.

La utilización del módulo de cristal líquido debe comenzar con la inicialización del controlador, en modo de 4 bits se requieren los siguientes pasos:

1. Escribir 0x3 en los cuatro bits, enviar pulso a señal E y esperar.

2. Escribir 0x3 en los cuatro bits, enviar pulso a señal E y esperar.

3. Escribir 0x3 en los cuatro bits, enviar pulso a señal E y esperar.

4. Escribir 0x3 en los cuatro bits, enviar pulso a señal E

5. Escribir 0x2 en los cuatro bits para habilitar modo de 4 bits, enviar pulso a señal E y esperar.

Después se puede enviar las instrucciones pertinentes para activar y borrar el display.

Los caracteres que se puede enviar al módulo son un subconjunto del código ASCII, ver Tabla 3-3, además se pueden definir símbolos nuevos escribiendo en el área de la memoria RAM correspondiente al generador de caracteres.

47

3.4 Utilización del protocolo TCP/IP en sistemas embebidos

El poder utilizar un protocolo estándar como es TCP/IP, bien documentado y con soporte en las más diversas plataformas de hardware y software, en sistemas embebidos manejados por microcontroladores cada vez más complejos y económicos, abre un abanico de posibilidades para cualquier diseñador de sistemas electrónicos. Por ejemplo poder controlar o monitorear un sistema desde cualquier navegador de Internet, desde cualquier lugar en que se tenga acceso a Internet, o permitir que el mismo sistema se comunique por e-mail para indicar algún suceso especial.

Los circuitos integrados disponibles permiten con un mínimo de componentes y costo proveer esta capacidad a cualquier sistema, ya existen microcontroladores que incorporan un puerto de red en el mismo circuito. Lo que resta por definir al diseñador es elegir entre utilizar un sistema operativo de tiempo real para el microcontrolador y programar el protocolo y el driver para el dispositivo de red o implementar las rutinas directamente en el microcontrolador, la principal dificultad de esto radica en la generación de los eventos a intervalos de tiempo precisos y manejar varios procesos en memoria.

Como referencia para el resto del capítulo se muestra el modelo de referencia Internet y su equivalencia con el modelo ISO/OSI.

Figura 3-18 Modelo ISO/OSI versus modelo Internet

3.4.1 El hardware para sistemas embebidos con conexión ethernet

Haciendo referencia al modelo Internet se debe proveer la capa de red, es decir, la capa física y de acceso al medio en el modelo ISO. Dentro de los protocolos de esta capa se pueden mencionar PPP (poin to point protocol),

Capa de aplicación

Capa de presentación

Capa de sesión

Capa de transporte

Capa de red

Capa de enlace de datos

Capa física

Capa de aplicación

Capa de transporte

Capa de Internet

Capa de red

48

que se puede utilizar en comunicaciones telefónicas, utilizando un módem que se conecte al microcontrolador por medio de sus puertos seriales.

Otro protocolo más interesante desde el punto de vista de la conectividad es el protocolo ethernet. La forma más fácil de conectar un microcontrolador al medio es mediante un controlador dedicado que se encargue de manejar la capa física y de acceso al medio, es decir que provea la capa de red del modelo Internet.

De estos dispositivos los más adecuados para interconectarse con un microcontrolador, debido al número de pines requeridos para la comunicación son los que se comunican mediante un bus ISA estándar, y específicamente aquellos que pueden utilizar un modo especial en que los datos de 16 bits que utilizan se pueden transmitir mediante 8 bits transmitiendo la mitad de la palabra en forma secuencial. Se puede mencionar dos controladores ampliamente utilizados en sistemas con microcontrolador: el RTL8139 de Realtek y el CS8900A de Cirrus Logic, ambos comparten características similares en cuanto a conexiones, requerimiento de componentes externos y registros internos de control, diferenciándose en el juego de instrucciones que proveen. Su interconexión al medio ethernet se realiza mediante transformadores de aislación y un conector RJ45.

También se puede agregar que existen módulos que incorporan el conector RJ45 con los transformadores de aislación, por lo que el sistema completo se puede reducir a sólo 3 componentes principales: el microcontrolador, el controlador ethernet y el módulo RJ45, más algunas componentes externas. Debido a lo anterior el costo de agregar conectividad a Internet a un sistema es bastante reducido.

En la tarjeta de desarrollo disponible se encuentra integrado un controlador CS8900A de Cirrus Logic, su esquema se muestra en la Figura 3-19.

49

Figura 3-19 Diagrama esquemático del CS8900A

Este circuito se encarga del acceso al medio ethernet en modo 10Base-T full duplex y se conecta directamente a los puertos de entrada y salida digitales del microcontrolador. Además contiene 4 KB de memoria RAM que sirven de buffer para el almacenamiento temporal de paquetes recibidos o enviados

La conexión al microcontrolador se realiza mediante 14 señales conectadas a los puertos 3 y 5. Un esquema de la conexión se muestra en la Figura 3-20.

Figura 3-20 Interconexión microcontrolador a controlador ethernet

Una ventaja del CS8900A es que viene en versiones de 3 y 5 V por lo que se puede utilizar sin problemas con la familia de microcontroladores MSP430.

4

8 D[7..0]

A[3..0]

IOW

IOR

MSP430F149

CS8900A

50

De las hojas de características del CS8900 se desprende que al utilizar el dispositivo en modo de 8 bits, es decir, pensando en conectarlo con un microcontrolador, las interrupciones no funcionan por lo que el software debe interrogar a intervalos regulares al controlador para saber si hay nuevos datos disponibles.

51

3.4.2 El software del microcontrolador

Dado que el controlador ethernet se encarga de la transmisión de los paquetes en el medio, el microcontrolador debe formar las tramas ethernet, es decir, incorporar la información sobre las direcciones físicas de los dispositivos, para ello debe implementar el protocolo de resolución de direcciones (ARP), debe programarse la comunicación entre el microcontrolador y el controlador a bajo nivel, además se debe implementar los protocolos de la capa de Internet y de transporte que requiera la aplicación.

Además del protocolo Internet (IP) se podría implementar partes o todas las funciones del protocolo de mensajes de Internet (ICMP) que facilitarían la resolución de problemas de conexión.

Acompañando a la tarjeta de desarrollo Easyweb se cuenta con el código fuente de un limitado stack de protocolos TCP/IP desarrollado por Texas Instruments [11], que provee una interfaz de programación para desarrollar aplicaciones de red.

Específicamente los protocolos implementados son los siguientes:

Ethernet

El microcontrolador sólo debe encargarse de formar las tramas ethernet, es decir, incorporar en un paquete de hasta 1500 bytes información sobre las direcciones físicas de los controladores, generar código de detección de errores y empaquetar y desempaquetar información proveniente de la capa de Internet. A su vez se comunica físicamente con el controlador de red por lo que debe programarse las funciones para configurar el controlador, conocer la dirección a la que responde y los registros que se debe escribir. El resto del protocolo ethernet: detección de colisión, acceso al medio, y otros los realiza el controlador ethernet, así como la interfaz con el medio físico.

Protocolo de resolución de direcciones, ARP

El objetivo de este protocolo de la capa Internet es traducir direcciones lógicas de Internet en direcciones físicas de dispositivos de red conectados al medio ethernet, para incorporar esta información en los paquetes ethernet.

52

Para ello el software utiliza dos mensajes: ARP Request para conocer la dirección de otro dispositivo y ARP Reply para responder a los requerimientos de otro dispositivo de red.

Protocolo Internet, IP

Este protocolo de la capa Internet se encarga de transmitir información entre los protocolos de transporte y el de ethernet, contiene información sobre la dirección lógica (direcciones IP) de los puntos de origen y destino, además se ocupa de fragmentar grandes flujos de datos en paquetes más pequeños que puedan ser transferidos por el protocolo ethernet. En este nivel cada paquete es tratado como una unidad independiente, sólo se asegura el encabezado de información IP con un código de verificación de errores, pero no se asegura que los datos sean transportados libres de errores o que lleguen en el orden correcto si son fragmentados.

Protocolo de mensajes de control de Internet, ICMP

Este protocolo de capa Internet se utiliza para obtener información acerca de la fiabilidad de la conexión, o de la causa de la falla de ésta. En el caso del stack TCP/IP disponible sólo se responde al mensaje Echo Request, al que se responde con un Echo Reply.

Protocolo de control de transmisión, TCP

Este es el único protocolo de transporte disponible en el código disponible. Este protocolo provee un medio confiable de transmisión de datos, se asegura la llegada de cada paquete y en el orden correcto, lo que se logra asignando un número de secuencia a cada paquete y requiriendo que a cada paquete transmitido el receptor responda con una señal de aceptación.

Antes de comenzar la transmisión con este protocolo se debe realizar una conexión entre el servidor el cliente mediante el intercambio de ciertos paquetes en los que se acepta la conexión por parte del servidor y se sincronizan los números de secuencia de los paquetes que se envían posteriormente.

53