PPTarquitectura de procesador cisc

-

Upload

anthony-blas-aldude -

Category

Documents

-

view

227 -

download

0

Transcript of PPTarquitectura de procesador cisc

-

7/24/2019 PPTarquitectura de procesador cisc

1/29

ARQUITECTURA DELPROCESADOR CISC

-

7/24/2019 PPTarquitectura de procesador cisc

2/29

ARQUITECTURA DEL PROCESADMC68000 CISC

Fue diseado desde cero con el n de !ro!orcionar"ui#ec#ura "ue $usca res#ricciones % "ue no seco&!a#i$les con diseos an#eriores del !rocesad

Lo "ue si $usca es la co&!a#i$ilidad de un ar"ui

en es#a 'acia adelan#e

-

7/24/2019 PPTarquitectura de procesador cisc

3/29

El a!or#e "ue ses#a ar"ui#ec#u

las an#i(uas eses#e !er&i#e u!eri*+ricos e,isen el &68000

-

7/24/2019 PPTarquitectura de procesador cisc

4/29

-

7/24/2019 PPTarquitectura de procesador cisc

5/29

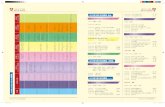

PROCESADOR CISC -. /ITS

RUMORES

Se !redeca "ue seria un MC68000 con de -. $i#s si&!le&en#e co&!le#os % $us

direcciones

Un &e1or rendi&ien#o

Las nue2as carac#ers#icas "ue #endran

-

7/24/2019 PPTarquitectura de procesador cisc

6/29

La idea era a&!liar los au#o$uses !ero ensu ins!ecci3n *ue un #ra&!oln &u% sensi$le"ue du!lica el anc'o de $anda del $us deda#os dis!oni$les

Se denomina bus, al conjunto de conexiones fsicas (cables,placa de circuito impreso, etc.) que pueden compartirse conmltiples componentes de hardware para que secomuniquen entre s.

El propsito de los buses es reducir el nmero de rutasnecesarias para la comunicacin entre los distintoscomponentes, al reali!ar las comunicaciones a tra"#s de unsolo canal de datos. $sta es la ra!n por la que, a "eces, se

utili!a la met%fora &autopista de datos&.

#odo es#o de$ido a la u#ili)aci3n &as *recuen#ede #a&ao de da#os &as !e"ueos4

Lue(o a!areci3 el MC680.0 "ue *ue anunciada

en 587 "ue sor!rendio a &uc'os con suco&!le1idad !o#encia % rendi&ien#o

-

7/24/2019 PPTarquitectura de procesador cisc

7/29

INTRODUCCION A LATECNOLOGIA HCMOS

Es un diseo de &icro!rocesador

Fue el !rinci!al ca#ali)ador !ara el e"ui!o de diseo REED9encar(ada !ara el !rocesador M68000 de -. $i#s4

Es#a nue2a #ecnolo(a o*rece (eo&e#ra de #ransis#ores &as

!e"ueos4

El !roceso :CMOS #enia o#ra 2en#a1a era ca!as de so!or#ar2elocidades de relo1 &u% su!eriores % !er&i#io "ue el !rocecons#ruira a las re(las del diseo 56 M:; es#o *ue el do$le2elocidad "ue 'as#a ese en#onces el es#

-

7/24/2019 PPTarquitectura de procesador cisc

8/29

RETOS ARQUITECTONICOS

La velocidad de reloj>#a&$i+n deno&inada cicorres!onde al n@&ero de !ulsos !or se(undoe,!resados en :er#) >:)?4 De es#e &odo un ordde .00 M:) !osee un relo1 "ue en2a .004000400!ulsos !or se(undo4 Por lo (eneral la *recuencia

es un &@l#i!lo de la *recuencia del sis#e&a >'SSide uso /us de la Par#e Fron#al?

-

7/24/2019 PPTarquitectura de procesador cisc

9/29

EEMPLO DE PUERTAS DE TU/ERIA B RETRASO EETAPAS

-

7/24/2019 PPTarquitectura de procesador cisc

10/29

-

7/24/2019 PPTarquitectura de procesador cisc

11/29

EL COFLICTO en#re los da#os % la ins#rucci3n acceduna sola co&unicaci3n !or el $us % #a&$i+n causas&is&o re#raso de #u$eras

El re#raso causado a #ra2+s de los cULA? % usando

2elocidad del relo1 &as r

Al no #ener "ue co&!ar#ir una >ULA? en#re las e#a!are#raso de calculo !odran reducirse % el relo1 seria ra!ido

-

7/24/2019 PPTarquitectura de procesador cisc

12/29

A #odo es#oEl !rocesador CISC

Dire&os "ue #iene una&e&oria a la ar"ui#ec#ura"ue !er&i#e la &ani!ulaci3ndirec#a de da#os en la

&e&oria e,#erna sin #ener"ue u#ili)ar los re(is#rosin#ernos *ache + es la memoria de acceso

r%pido de una computadora queuardan temporalmente los datosde memoria

-

7/24/2019 PPTarquitectura de procesador cisc

13/29

Es#e !rocesador ali&en#a desde un cac'ein#erno

Mien#ras "ue una ins#rucci3n se es#a &o2ieda#os a la &e&oria e#erna co&o la ul#i&a ede e1ecuci3n la si(uien#e ins#rucci3n se !ue

car(ar en la #u$era

-

7/24/2019 PPTarquitectura de procesador cisc

14/29

Puede en#onces ser e1ecu#ado usando las e#a!as de &odo de inac#i2idad de la #u$era co&o se &ues#ra

Es#o !er&i#ir< "ue las

ac#i2idades de #u$era!uedan ser do$ladas % lasu!er!osici3n deins#rucciones resul#an#es deel resul#ado de la e1ecuci3ncero ciclos de relo1 % un

rendi&ien#o inni#o

En realidad el #ie&!o dee1ecuci3n se ocul#a en lu(arde reducirse a nada

-

7/24/2019 PPTarquitectura de procesador cisc

15/29

El estndar de rendiiento de !" #its MC$

El MC680.0 *ue lan)ado en a$ril de 587 co&o ees#

-

7/24/2019 PPTarquitectura de procesador cisc

16/29

Fue un 2erdadero !rocesador de-. $i#s con $uses de da#os %direcciones e,#ernas de anc'o -.

$i#s co&o se &ues#ra Una cac'+ de ins#rucciones % una

!alanca de ca&$ios $arril !arareali)ar o!eraciones de ca&$iode al#a 2elocidad se incor!oraron

den#ro del c'i! !ara !ro!orcionara!o%o a es#as *unciones

-

7/24/2019 PPTarquitectura de procesador cisc

17/29

Caracteristicas

La &e&oria 2ir#ual % la con#inuaci3n de ins#ruccio

eran so!or#ado4

Las seales de $us % de con#rol *ueron si&ilares asus !redecesores M68000 "ue o*rece una in#er*a)&e&oria asncrona !ero con una o!eraci3n de #re

ciclos > en 2e) de cua#ro ? % di&ensiona&ien#o $udin

-

7/24/2019 PPTarquitectura de procesador cisc

18/29

El dia(ra&a de $lo"ues in#erno &ues#ra la loso

$

-

7/24/2019 PPTarquitectura de procesador cisc

19/29

El con#rolador de $us % elsecuenciador a'ora!ueden *uncionar

inde!endien#e&en#e unodel o#ro !er&i#iendo "uelos da#os si&ul#

-

7/24/2019 PPTarquitectura de procesador cisc

20/29

La #u$era real u#ili)adoes $as#an#e sos#icadode cua#ro e#a!as con laconsis#e en un enca&inins#rucciones "ue ace!

%a sea el con#rolador do el cac'+ in#erna4 Co&ins#rucci3n es !rocesad#u$era los da#os in#er&!ueden o $ien causar &c3di(os secuencias "ue!ara con#rolar la unidad

e1ecuci3n o en el caso ins#rucciones &

-

7/24/2019 PPTarquitectura de procesador cisc

21/29

Modelo de usuario del !ro(ra&ador es e,ac#a&e&is&o "ue !ara el MC68000 MC68050 % MC680Tiene las &is&as oc'o da#os % las oc'o direccio-. $i#s or(ani)aci3n re(is#radora4 El &odo de sues un su!e con1un#o de sus !redecesores4 Dis!o#odos los re(is#ros "ue se encuen#ran en sus

!redecesores ade&

-

7/24/2019 PPTarquitectura de procesador cisc

22/29

El su!er2isor u#ili)a %a sea su!un#ero de !ila &aes#ro oin#erru&!ir !un#ero de !ilade!endiendo de la causae,ce!ci3n % el es#ado del $i# M enel re(is#ro de es#ado4 Si es#e $i#

es#< claro #odas las o!eracionesde !ila !or de*ec#o al !un#ero de!ila de la AG4

Si se es#a$lece &arcos de !ila dein#erru!ci3n se al&acenanu#ili)ando el !un#ero de !ila dein#erru!ci3n &ien#ras o#ras

o!eraciones u#ili)an el !un#ero del&aes#ro4 Es#o !er&i#ee*ec#i2a&en#e el sis#e&a !ara&an#ener dos !ilas se!aradas4Aun"ue !rinci!al&en#e !araso!or#e del sis#e&a o!era#i2o es#ere(is#ro adicional se !uede u#ili)ar!ara diseos de al#a a$ilidad4

INTERFACES DEL BUS

-

7/24/2019 PPTarquitectura de procesador cisc

23/29

Muc'as de las seales &os#radas en el dia(ra&ade !ines a ca$o son los &is&os "ue los de laMC68000 los c3di(os de *unci3n FC0 . los!asadores de in#erru!ci3n IPL0. % los !asadoresde solici#ud de $us de RESET H :ALT % /ERR reali)an las &is&as *unciones 4

Con la desa!arici3n de la in#er*a) de es#iloM6800 seales se!aradas se u#ili)an !ara indicarun au#o co&o 2ec#or de in#erru!ci3n4

La seal AJEC se u#ili)a !ara es#a *unci3n %!uede ser ar&ado de *or&a !er&anen#e si sere"uieren las in#erru!ciones s3lo Au#o&

-

7/24/2019 PPTarquitectura de procesador cisc

24/29

!su!erior e in*erior M68000 'an sidosus#i#uidos !or AO % los dos!asadores de #a&ao SI;E0 %SI;E54 Es#os indican la can#idad deda#os de i)"uierda a #rans*erir en elciclo de $us ac#ual % cuando se

u#ili)a con $i#s de direcci3n A0 % A'!uede !ro!orcionar in*or&aci3n dedescodicaci3n de &anera "ue los$%#es correc#a den#ro del $us deda#os a&!lia 7 $%#e se !uedenac#i2ar4

La seal de edad DTACK H 'a sidoree&!la)ado !or dos nue2osDSACK0 % DSACK54 Ellos!ro!orcionan la an#i(ua *unci3nDTACK indicando un ciclo de $use,i#oso % se u#ili)an en eldi&ensiona&ien#o $us din

-

7/24/2019 PPTarquitectura de procesador cisc

25/29

La &a%ora de los sis#e&as dis!oni$les en la in#roducci3MC680.0 eran o 8 o 56 $i#s de #a&ao4 Incluso los dise$asan en el *or&a#o de 56 $i#s aun"ue 'o% en da es a&

ace!#ado % u#ili)ado en su *or&a#o *ull-.$i#4 El !ro$le&ain#en#o de co&$inar 8 56 % -. ru#as de da#os $i#4 El !ro!uede so!or#ar es#e #i!o de *or&a e,!lci#a den#ro de suins#rucciones de lo "ue el so*#are !odra 2erse o$li(adode#er&inados #a&aos de da#os con cier#os ran(os de d

El Di&ensiona&ien#o $us din

-

7/24/2019 PPTarquitectura de procesador cisc

26/29

Una 2e) &

-

7/24/2019 PPTarquitectura de procesador cisc

27/29

El cac'e de instr(cciones

Uno de los !ro$le&as !erennes "ue en*ren#a cual"uier diselen#o acceso a la &e&oria4 A &enudo un !rocesador !uedeins#rucciones &uc'o & El MC680.0 du!lic3 la 2elocidad de relo1 del !rocesador a 5

duran#e la noc'e % redu1o un ciclo de $us MC68000 !or .a -4 Por es#

-

7/24/2019 PPTarquitectura de procesador cisc

28/29

Se aadi3 el cac'+ de ins#rucciones de .6 $%#es in#erna del MC680.0e2i#ar la de(radaci3n es!erada den#ro de un sis#e&a con un rendi&ien&e&oria !o$re4

Con#iene alrededor de 500 ins#rucciones % se or(ani)a co&o una &a#ri

7 $%#es4

El acceso a las ins#rucciones de la cac'+ !uede ocurrir si&ul#

-

7/24/2019 PPTarquitectura de procesador cisc

29/29

El sis#e&a de cac'+ de *unciona&ien#o es &u% sencillo4 Cuando unins#rucci3n se inicia la direcci3n se su&inis#ra al con#rolador de $u

cac'+4 Si los da#os es#< !resen#e en la &e&oria cac'+ una seal de acier#

i&!ide "ue el con#rolador de $us de con#inuar el ciclo de $us e,#ernciclo es#< en realidad nunca co&en)3 !or"ue el Nas' elec#r3nico Aar&a4? Si los da#os no se al&acena en cac'+ se !roduce un *allo e,#erno con#in@a % la ins#rucci3n se o$#iene de &e&oria e,#erna4

Una co!ia de la ins#rucci3n se u#ili)a !ara ac#uali)ar la cac'+ in#ernsu&inis#ro de la direcci3n #an#o al con#rolador de $us % la &e&oria