Actividad Complementarias_U1_Electronica

-

Upload

richard-barrantes -

Category

Documents

-

view

18 -

download

1

description

Transcript of Actividad Complementarias_U1_Electronica

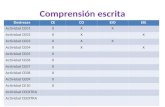

ACTIVIDADES COMPLEMENTARIASUnidad 1. Circuitos secuenciales básicos

Una vez finalizadas las dos actividades complementarias de esta unidad, comprima el archivo en formato zip o rar, dando clic derecho al archivo, Enviar a, Carpeta comprimida. Luego envíelas a su facilitador a través del medio utilizado para tal fin en el curso.Actividad complementaria 1Llenar las siguientes tablas correspondientes al funcionamiento de cada uno de los siguientes circuitos secuenciales. Tenga en cuenta los simuladores que se encuentran en los contenidos de la unidad 1, allí encontrará la manera de realizar la verificación de circuito combinacional, tabla de verdad y diagrama de tiempos de cada circuito secuencial.

Funcionamiento de latch SR con entrada activa en nivel alto

Circuito combinacional

Ubica las entradas R y S y las salidas Q y Q (escribiendo en las casillas en blanco) en el siguiente diagrama.

Tabla de verdad

Llena la tabla de la verdad de acuerdo al comportamiento de las entradas Entradas

salidas Comentario de funcionamiento

S R Q Q0 0 NC NC El latch permanece en el mismo

estado0 1 0 1 Latch se pone a RESET1 0 1 0 Latch se pone a SET1 1 0 0 Condición no valida (funciona.

inapropiado)

Diagrama de tiempos

Raye el cronograma de acuerdo al comportamiento de la tabla de verdad. Ejemplo de cómo llenar la cuadricula del diagrama de tiempos

1

S

R

Q

Q

Funcionamiento de latch SR con entrada activa en nivel Bajo

Circuito combinacional

Ubica las entradas R y S y las salidas Q

y Q (escribiendo

en las casillas en blanco) en el siguiente diagrama.

Llena la tabla de la verdad de acuerdo al comportamiento de las entradas

Entradas

salidas Comentario de funcionamiento

S R Q Q0 0 X X Condición no valida (función. inapropiado)0 1 1 0 Latch se pone a SET1 0 0 1 Latch se pone a RESET1 1 NC NC El latch permanece en el mismo estado

Raye el cronograma de acuerdo al comportamiento de la tabla de verdad. Ejemplo de cómo llenar la cuadricula del diagrama de tiempos

2

S

R

Q

Q

Funcionamiento de latch SR con entrada activa de validación

Circuito combinacional

Ubica las entradas E, R y S y las salidas Q y Q (escribiendo en las casillas en blanco) en el siguiente diagrama.

Tabla de verdad

Llena la tabla de la verdad de acuerdo al comportamiento de las entradas

Entradas salidas Comentario de funcionamientoE S R Q Q1 0 0 x x El latch permanece en el mismo

estado1 0 1 0 1 Latch se pone a RESET1 1 0 1 0 Latch se pone a SET0 1 1 NC NC Condición no valida(func. Inaprop.)

Diagrama de tiempos

Raye el cronograma de acuerdo al comportamiento de la tabla de verdad. Ejemplo de cómo llenar la cuadricula del diagrama de tiempos

3

QS

E

R

Q

Actividad complementaria 2Llenar las siguientes tablas correspondientes al funcionamiento de cada uno de los siguientes circuitos secuenciales. Tenga en cuenta los simuladores que se encuentran en los contenidos de la unidad 1, allí encontrará la manera de realizar la verificación de circuito combinacional, tabla de verdad y diagrama de tiempos de cada circuito secuencial.

Funcionamiento de latch DCircuito combinacional

Ubica las entradas E y D y las salidas Q y Q (escribiendo en las casillas en blanco) en el siguiente diagrama.

4

Tabla de verdad

Llena la tabla de la verdad de acuerdo al comportamiento de las entradas

Entradas

salidas Comentario de funcionamiento

E D Q Q1 0 0 1 Latch se pone a RESET1 1 1 0 Latch se pone a SET0 X NC NC El latch permanece en el mismo estado

Diagrama de tiempos

Raye el cronograma de acuerdo al comportamiento de la tabla de verdad. Ejemplo de cómo llenar la cuadricula del diagrama de tiempos

Funcionamiento de Flip-Flop SR

Circuito combinacional

Ubica las entradas CLK, S y R y las salidas Q y Q (escribiendo en las casillas en blanco) en el siguiente diagrama.

5

QCLK

S

RQ

QE

DQ

Tabla de verdad

Llena la tabla de la verdad de acuerdo al comportamiento de las entradas Entradas salidas Comentario de

funcionamientoS R CLK Q Q0 0 X X X Permanece en el mismo estado0 1 ↑ 0 1 RESET1 0 ↑ 1 0 SET1 1 ↑ NC NC Condición No valida

Diagrama de tiempos

Raye el cronograma de acuerdo al comportamiento de la tabla de verdad. Ejemplo de cómo llenar la cuadricula del diagrama de tiempos

Funcionamiento de Flip-Flop Jk

Circuito combinacional

Ubica las entradas CLK, J y K y las salidas Q y Q (escribiendo en las casillas en blanco) en el siguiente diagrama.

Tabla de verdad

Llena la tabla de la verdad de acuerdo al comportamiento de las entradas

Entradas salidas Comentario de funcionamiento

J K CLK Q Q0 0 ↑ Qn-1 Qn-1 Sin Cambio

6

QCLK

S

RQ

0 1 ↑ 0 1 RESET1 0 ↑ 1 0 SET

1

1 ↑ Qn-1 Qn-1 Bascula

Diagrama de tiempos

Raye el cronograma de acuerdo al comportamiento de la tabla de verdad. Ejemplo de cómo llenar la cuadricula del diagrama de tiempos

Actividad complementaria 3Realice una lista de aplicaciones donde estén implícitos los flip-flop tipo D, T y maestro-esclavo.

Aplicaciones de Flip-Flop

Flip-Flop AplicacionesTipo D

En registros de corrimiento, cerradura digital, dispositivos de memoria, contadores, circuito Monoestable, Llaves oscilante, etc.

Tipo TContadores asíncronos binarios, divisor de frecuencia

7

Maestro-esclavo Dimer, circuitos de control.

8